## **Homework Assignment #4**

Problem 1 a) Design a FD amplifier with two stages for the following specs using 0.13 µm technology

V<sub>DD</sub> = 1.2V or V<sub>DD</sub> =  $-V_{SS} = 0.6V$ SR > 2V/µ sec  $A_{o,DC} \ge 90dB$ DC CMRR ≥ 85dB GBW > 4MHz PM > 60° C<sub>L</sub>//R<sub>L</sub> = 25pF//47KΩ Power to be minimum 1% T<sub>s</sub> < 160nS

Describe your design procedure for the differential and common-mode gains and bandwidths. Use two different CM detectors and compare results. Provide a summary table including IIP3, 1% THD and indicate the bandwidths and gains of  $A_{DM}$  and  $A_{CM}$ .

- b) Provide the output step response for a common-mode step of 0.5V. What is the Ts?

- c) Force a transistor mismatch of 2% in the differential pair and study its effects on the performance. In particular the linearity.

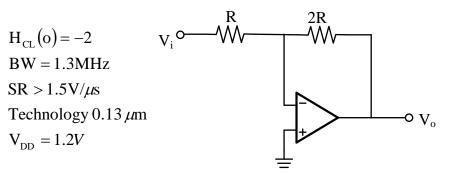

- Problem 2. Design the single output op amp to meet the following specs when it is connected as an inverter amplifier. Describe procedure to set the op amp specs.

The accuracy error of the DC gain of the inverter should be less than 1.1%

- What are poles and zero locations?

- What is ROC and phase margin?