## Low Voltage Analog Circuit Design Techniques:

A Tutorial

## IEEE Dallas CAS Workshop 2000

Edgar Sánchez-Sinencio

http://amsc.tamu.edu/

March 27, 2000

Texas A&M University

Analog and Mixed-Signal Center

# Low Voltage Analog Circuit Design Techniques: Roadmap

Low voltage (LV) power supply circuit design techniques are addressed in this tutorial. In particular:

(i) Introduction;

(ii) Transistor models capable to provide performance and power consumption tradeoffs;

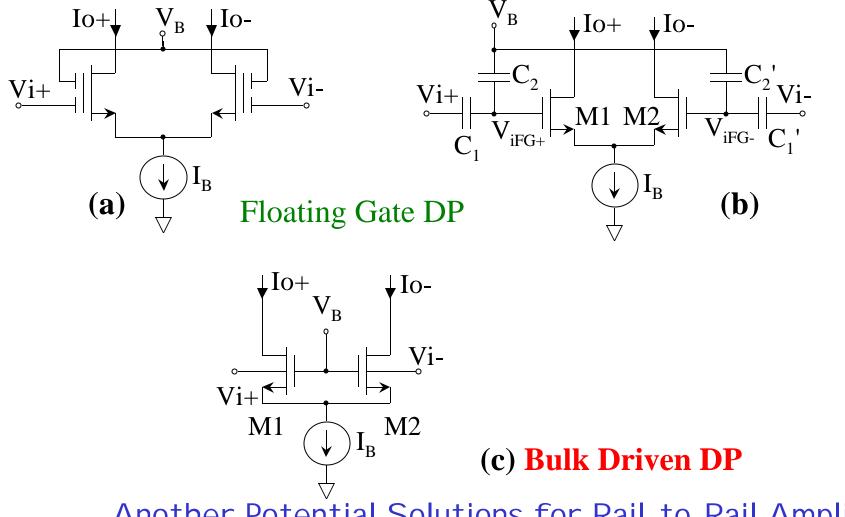

(iii) Low voltage implementation techniques, such as floating gates and bulk driven;

(iv) Basic building blocks not involving cascode structures, and

(v) LV circuit implementations examples.

# Motivation

The need for analog circuits in modern mixed-signal VLSI chips for multimedia, perception, control, instrumentation medical electronics and telecommunication is very high.

- What are the challenges in designing low voltage circuits ?

- To operate with power supplies smaller than 3.3 volts

- To design circuits with the same performance or better than circuits designed for larger power supplies

- To perform with technologies smaller than 0.5 micron

- -To come with new design alternatives,

- Why are we concerned in designing low voltage circuits ?

- Designers can not use conventional cascode structures, and other conventional design methodologies.

- Circuits should have the same performance or better than circuits designed for larger power supplies

- Circuit performance with technologies smaller than 0.5um must be better than circuits for larger technologies.

- -Third-generation communication applications require circuits ( and systems) with improved dynamic range over a much wider bandwidth.

- New building blocks and system must be designed to satisfy the needs of portable, lighter and faster equipment

# I ssues about low power supply voltage

• Threshold and VDSAT do not scale down linearly with power supply nor with smaller size technologies.

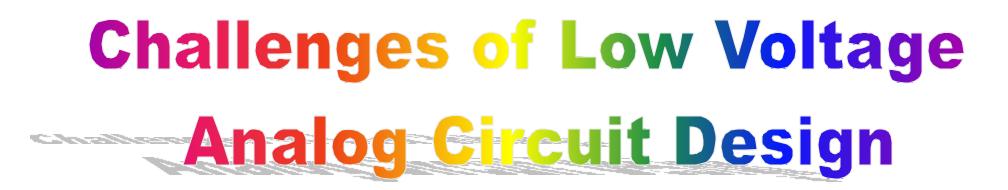

• Let us consider an illustrative example of a cascode and a simple inverting amplifiers, assume transistors MC and MS carry the same current IL, VT = 0.75V and VDS(SAT) = 0.2V

• Keeping the same output voltage swing for both circuits involve the tradeoffs shown in the plot of transistor sizes and GBW vs. Power Supply Voltage

(c)

# Transistor Regions of Operation

- How to determine how much bias current is needed for certain application ?

- When a designer operates transistors in saturation, what does it mean VDS > VDS(SAT) ?

• Can a circuit have their transistors operating in the transition region ? What transistor model equation can be employed ?

## **One Equation-All Regions Transistor Model**

- Features of ACM model:

- physics-based model,

- universal and continuous expression for any inversion,

- independent of technology, temperature, geometry and gate voltage,

- same model for analysis, characterization and design.

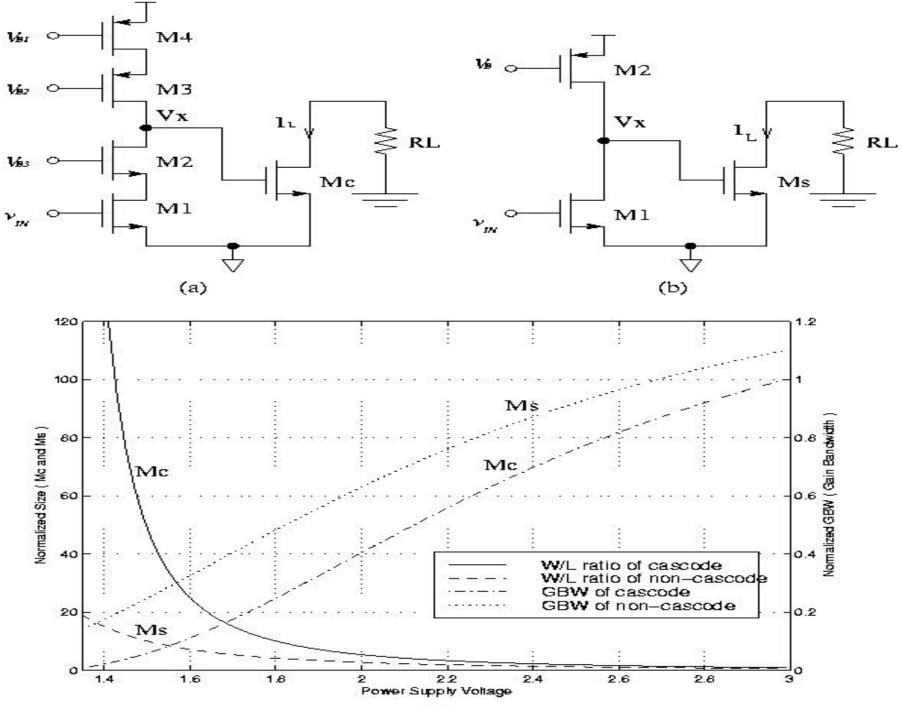

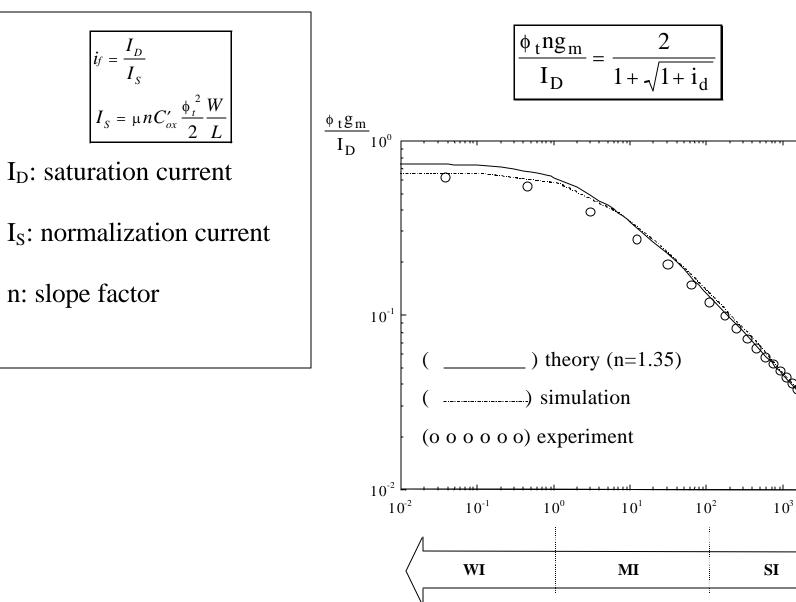

- Main design equations: (design parameters:  $I, g_m, i_f$ )

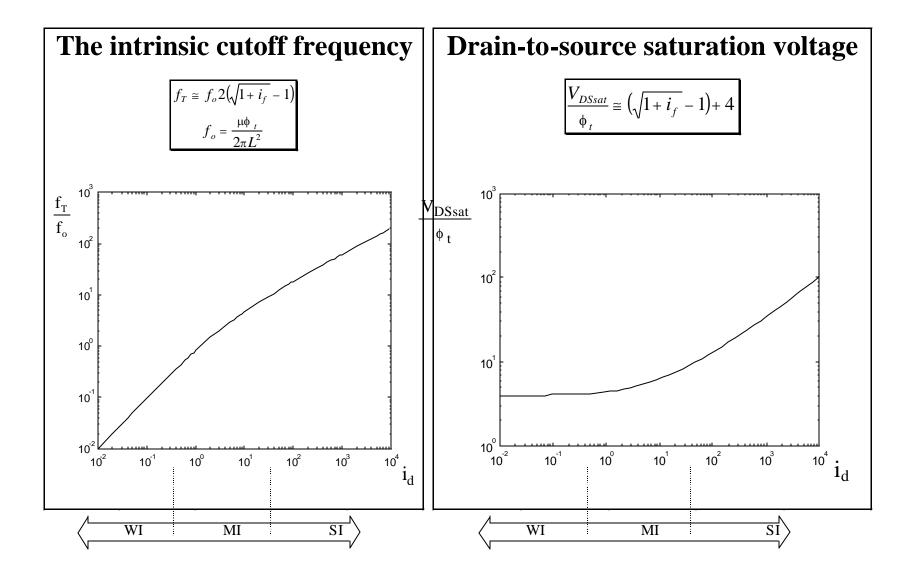

| $\frac{I}{\phi_t g_m n} = \frac{1 + \sqrt{1 + i_f}}{2}$ $f_T = \frac{\mu \phi_t}{2\pi L^2} 2\left(\sqrt{1 + i_f} - 1\right)$ $\frac{W}{L} = \frac{g_m}{\mu C_{ox} \phi_t} \frac{1}{\sqrt{1 + i_f} - 1}$ | I = drain current in transistor<br>$g_m = \text{transconductance in saturation}$<br>n = slope factor<br>$\phi_t = \text{thermal voltage}$<br>$i_f = I/I_s \qquad \text{, where}$<br>is the normalization current.<br>$I_s = \mu n C_{ox} \frac{\phi_t^2}{2} \frac{W}{L}$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\frac{V_{DSAT}}{\Phi_t} \cong \left(\sqrt{1+i_f} - 1\right) + 4$                                                                                                                                       | $i_f << 1$ — weak inversion,                                                                                                                                                                                                                                             |

| $\frac{W}{L} = \frac{g_m}{2\mu C_{ox} \phi_t \left(\frac{I}{\phi_t g_m n} - 1\right)}$                                                                                                                  | $i_f >> 1$ — strong inversion.                                                                                                                                                                                                                                           |

#### Normalized Current

#### Transconductance-to-Current Ratio

$10^{4}$

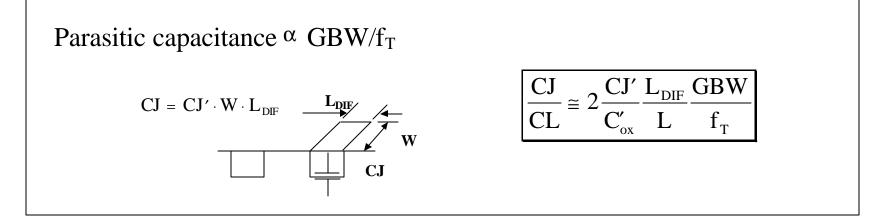

**Correlation Between Area and Frequency Response**

$$WL \cong 2 \frac{CL}{C'_{OX}} \frac{GBW}{f_{T}}$$

Correlation Between Junction Capacitance (CJ) and Frequency Response

|                                                                            | BIPOLAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC Circuit                                                                 | $ \begin{array}{c c}  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  &$ | $ \begin{array}{c c}  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  &$ |

| Transconductance<br>-to-current-ratio<br>(g <sub>m</sub> /I <sub>D</sub> ) | $I_{C} \phi_{t}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{g_{\rm m}}{I_{\rm D}} = \frac{1}{\phi_{\rm t}} \left( \frac{2}{n(1 + \sqrt{1 + i_{\rm d}})} \right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DC Gain<br>(A <sub>vo</sub> )                                              | $A_{vo} = -\frac{VA}{\phi_t}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A_{vo} = -\frac{VA}{\phi_t} \left( \frac{2}{n(1 + \sqrt{1 + i_d})} \right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Gain-Bandwidth<br>Product (GBW)                                            | $GBW = \frac{1}{2\pi CL} \frac{I_C}{\phi_t}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $GBW = \frac{1}{2\pi CL} \frac{I_{D}}{\phi_{t}} \left( \frac{2}{n(1 + \sqrt{1 + i_{d}})} \right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Intrinsic Cutoff<br>Frequency (f <sub>T</sub> )                            | $f_T \cong \frac{1}{2\pi\tau}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $f_{\rm T} \cong \frac{1}{2\pi\tau} 2\left(\sqrt{1+i_{\rm d}} - 1\right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Minimum Output<br>Voltage (V <sub>o</sub> )                                | $\frac{V_{CEsat}}{\phi_t} \cong 6 \text{ to } 8$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{V_{DSsat}}{\phi_t} = (\sqrt{1+i_d} - 1) + 4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# Low Voltage Analog Circuit Design Techniques: Roadmap

Low voltage (LV) power supply circuit design techniques are addressed in this tutorial. In particular:

(i) Introduction;

(ii) Transistor models capable to provide performance and power consumption tradeoffs;

(iii) Low voltage implementation techniques, such as floating gates, self-cascode, low voltage current-mirrors and bulk driven;

(iv) Basic building blocks not involving cascode structures, and

(v) LV circuit implementations examples.

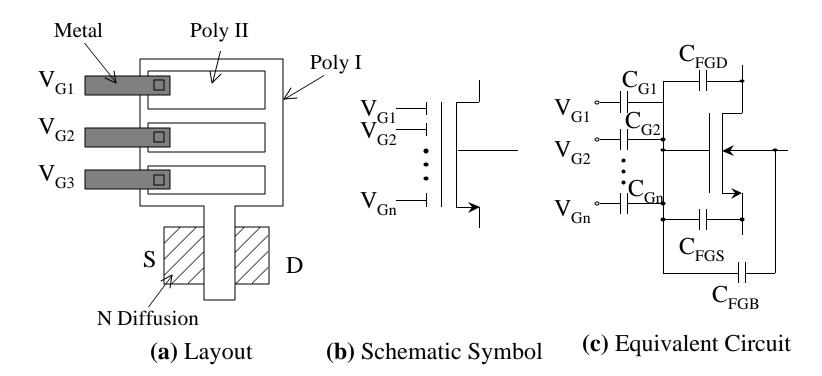

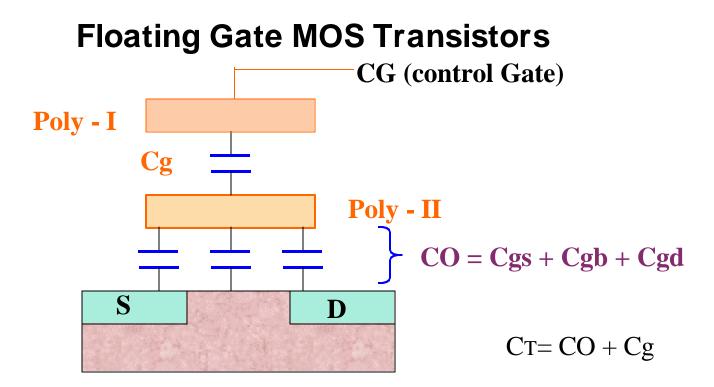

### Floating Gate Transistors

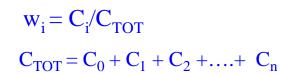

The floating gate voltage  $V_F$ , assuming that the initial charge  $Q_F$  in the floating gate is zero, is described by:

$$\mathbf{V}_{\mathbf{F}} = \mathbf{w}_0 \mathbf{V}_0 + \mathbf{w}_1 \mathbf{V}_1 + \mathbf{w}_2 \mathbf{V}_2 + \dots + \mathbf{w}_n \mathbf{V}_n$$

Where

Assuming Cg >> Cgd,Cgb, an approximate IDs can be obtained:  $IDs=K^{o}eff[(VCGS-VT,eff)VDS-CT VDS^{2}/2Cg]$  ohmic  $IDs=K^{s}eff(VCGS-VT,eff)^{2}$  saturation Where: VT,eff=VTCO-QFG/Cg

$K^{o}$ eff = Kp(Cg/CT)(W/L),  $K^{s}$ eff = Kp(Cg/CT)<sup>2</sup>(W/L),

What is the effect of the FG on the transconductance and the output conductance, in the saturation region ?

$gm = (2K^2 eff IDS)^2 = Cg g^c m/CT$  $go = g^c o + Cgd gm/Cg$

Where **g<sup>c</sup>m** and **g<sup>c</sup>o** are the conventional transconductance and the output conductance of the conventional MOS transistor.

Thus, the FGT has a smaller transconductance and a larger output conductance than conventional MOS transistor

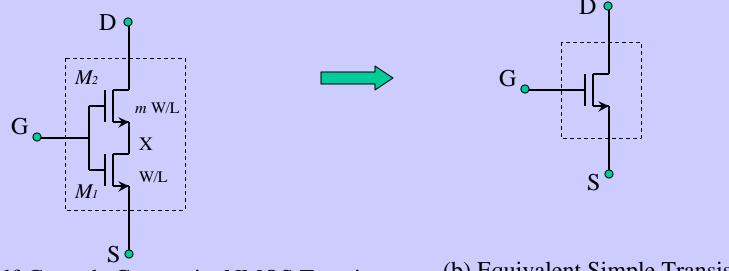

## What is a Self-Cascode Composite Transistor?

(a) Self-Cascode Composite NMOS Transistor

(b) Equivalent Simple Transistor

In practical cases, for optimal operation the W/L ratio of  $M_2$  should be larger than that of  $M_1$ , *i.e.* m > 1.

The 2-transistor structure can be treated as a composite transistor, which has a much larger effective channel length (thus lower output conductance).

The lower transistor  $M_1$  is equivalent to a resistor, but this resistor is input dependent.. The effective transconductance of the composite transistor is approximately equal to the transconctance of  $M_1:gm_{-eff}=gm2/m=gm1$

# Equivalent Transistor Parameter

For the composite transistor work in saturation region, we know  $M_2$  should in saturation and  $M_1$  is in linear region. Thus, we can write equations for these two transistors as:

$$i_1 = \frac{\beta_2}{2} (V_{GS} - V_X - V_T)^2$$

$i_1 = \beta_1 \left( V_{GS} - V_T - \frac{1}{2} V_X \right) V_X$

Solving  $i_1$  we can obtain:

From (3), we have  $\beta_{eq} = \frac{\beta_2 \beta_1}{\beta_2 + \beta_1}$

$$i_{2} = \frac{1}{2} \frac{\beta_{2}\beta_{1}}{\beta_{2} + \beta_{1}} (V_{GS} - V_{T})^{2}$$

If

$$\beta_2 = m \cdot \beta_1$$

$\beta_{eq} = \frac{m}{m+1} \beta_1 = \frac{1}{m+1} \beta_2$

$\beta_{eq} \Big|_{m-\infty} = \beta_1$

# Comments on VDSAT

Because transistor  $M_1$  always operates in linear region while the top transistor operates in saturation or linear region. Voltage between the source and drain terminal of  $M_1$  is so small that there is no discernable V<sub>DSAT</sub> difference in both the composite and simple transistors. Thus, self-cascode structure can be used in *low voltage applications*.

$$V_{DSAT - eq} = V_{DSAT - M2} + V_{DS - M1} = V_{DSAT - M2} + I_{D2}R_{M1}$$

where  $R_{M1} = \frac{1}{\mu C_{OX}(V_{GS} - V_T)\frac{W}{L}}$

The operating voltage of a regular cascode circuit is much higher than that of a single transistor. This characteristic makes regular cascode circuit not suitable for low voltage applications.

# References

- 1. C. Galup-Montoro, etc., "Series-Parallel Association of FET's for High Gain and High Frequency Applications", *IEEE JSSC*, Sept. 1994

- 2. D. Ceuster, etc., "Improvement of SOI MOS current-mirror performances using serial-parallel association of transistors", *Electronics Letters*, Feb. 1996

- 3. P. Furth, H. Om'mani, "A 500-nW Floating-Gate Amplifier with Programmable Gain", IEEE 1999

- 4. I. Fujimori, T. Sugimoto, "A 1.5V, 4.1mW Dual-Channel Audio Delta-Sigma D/A Converter", *IEEE JSSC*, Dec. 1998

- 5. Personal note from Dr. Ugur Cilingiroglu

- 6. Yunchu Li, examples and SPICE tables

- A.I.A. Cunha, M.C. Schneider, and C. Galup-Montoro, "An MOS transistor model for analog circuit design", *IEEE J. Solid-State Circuits*, vol. 33, No. 10, pp 1510-1519, Oct. 1998

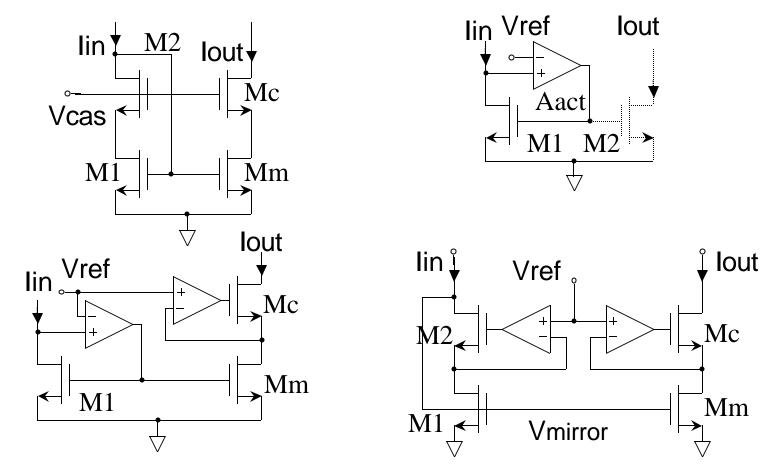

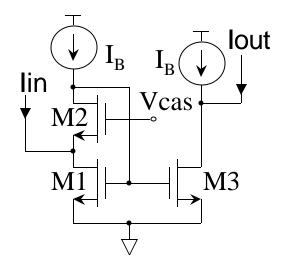

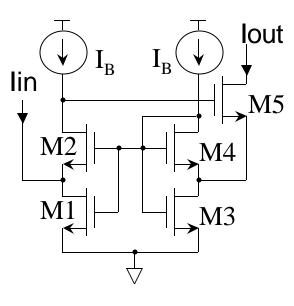

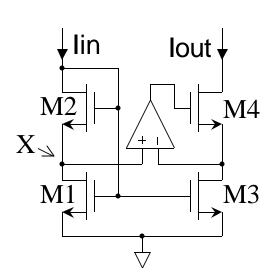

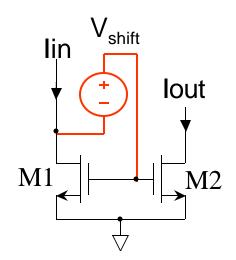

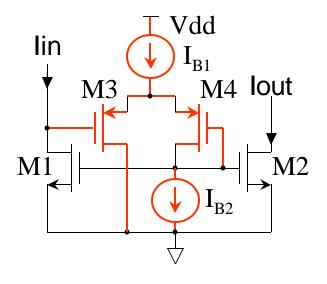

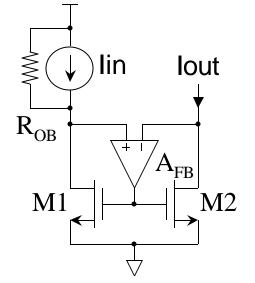

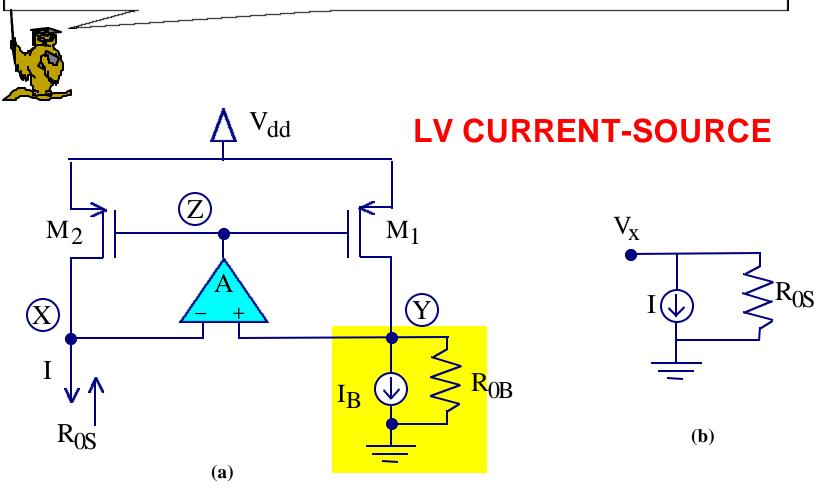

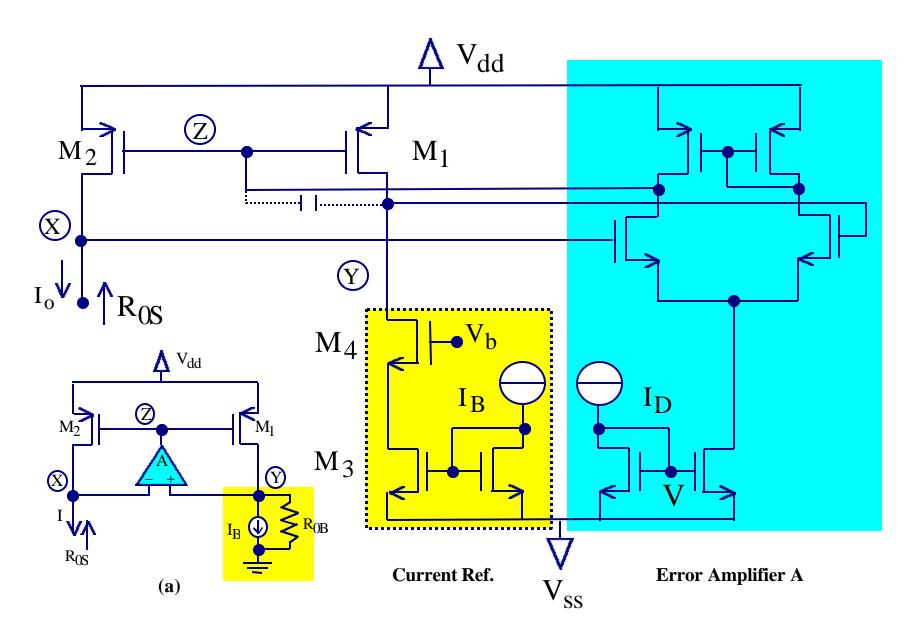

#### **Potential LV Current-Mirrors**

**Goals:** To reduce the input impedance and to increase the output impedance, while keeping the voltage operation

How can we obtain a large impedance and low head room for the tail current used in a differential pair ?

A conceptual Schematic of the low voltage current source. (a) Current source representation (b) Architecture

$$R_{os} = \frac{1 + g_{m1}A_o / (g_{o1} + g_{oB})}{g_{o2}(1 + A_o g_{m1} / (g_{o1} + g_{oB}) - A_o g_{m2} / g_{o2})}$$

(1)

where  $g_{m1}(g_{m2}), g_{01}(g_{02})$  are the transconductance and output conductance of  $M_1(M_2)$ , respectively.  $A_0$  is the DC gain of the error amplifier "A" and  $g_{0B}(R_{0B})$  is the output conductance (resistance) of the reference current source  $I_B$ . Assuming that  $g_{m1} = g_{m2}$  and  $g_{01} = g_{02}$ , equation (1) can be simplified as:

$$R_{\rm OS} \approx -R_{\rm OB} \tag{2}$$

Note that the resistance is negative and is equal to the resistance of the reference source  $I_B$ .

$$R_{\rm OS} \approx -\frac{g_{\rm m4}}{g_{\rm o3}g_{\rm o4}}$$

(3)

Full implementation of the LV current source.

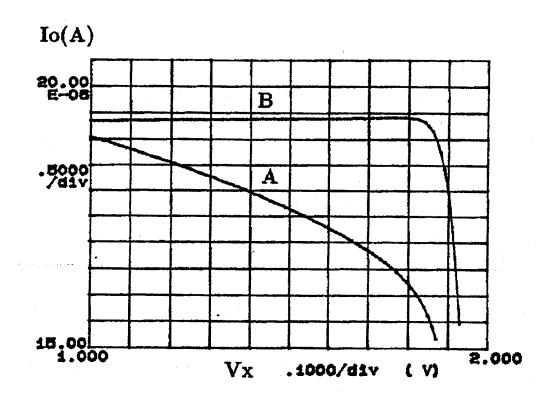

Measured output current of the simple (curve A) and LV (Curve B) current source.

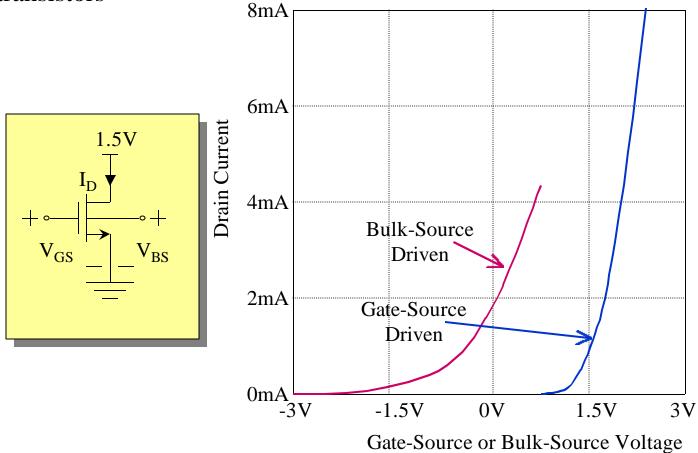

# Bulk-Driven MOS Transistor Characteristics

• I<sub>D</sub> vs. V<sub>BS</sub> or V<sub>GS</sub> of bulk-driven and conventional gate-driven MOS transistors

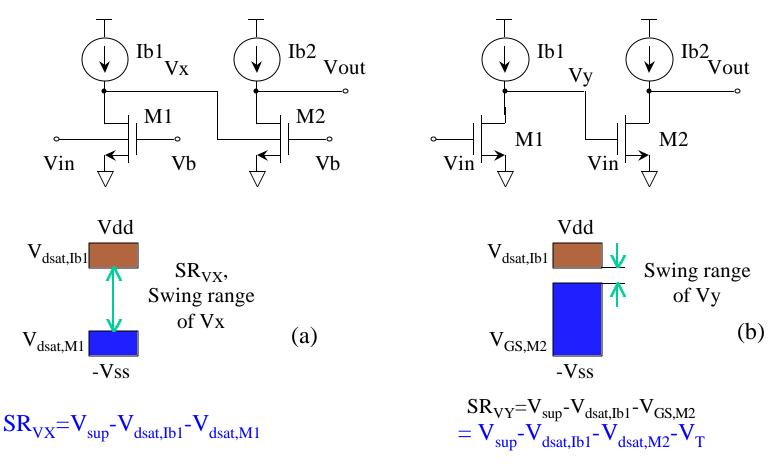

## **Overhead of Bulk-Driven MOS Transistors**

The bulk-driven amplifier is more suitable for low voltage operation. Please notice that the maximum allowable voltage at Vx is  $V_{DIODE}$ .

# Advantages of Bulk-Driven MOS Transistors

- The depletion characteristic allows zero, negative, and even small positive values of bias voltage to achieve the desired dc current. This can lead to larger input common mode voltage range and voltage swing that could not otherwise be achieved at low power supply voltages. (Please refer the following example in this section and bulk-driven differential pair discussed in following sections )

- We can use the conventional gate to modulate the bulk-driven MOS transistor.

- Example

Assume for the low voltage amplifiers, power supply voltage is

$V_{sup} = V dd + /V ss / < V_{DIODE} + V_{dsat}$  ,

where  $V_{\text{DIODE}}$  is the forward Si diode cut-in voltage.

The voltage swing of Vx (Figure a, the amplifier with bulk-driven MOS FETs) has only  $2V_{dsat}$ 's decrease over  $V_{sup}$ . In such a low voltage, the conventional gate-driven amplifier (Figure b) fails to operate or may be greatly limited in voltage swing.

## Disadvantages of Bulk-Driven MOS Transistors

- The transconductance of a bulk-driven MOS FET is substantially smaller than a conventional gate-driven MOS transistor. This may result in lower GBW and worse frequency response, but better linearity and smaller power supply requirements.

- For a conventional gate-driven MOSFET, the frequency response capacity is described by its transitional frequency,  $f_T$ ,

$$f_{T,gate-driven} = \frac{g_m}{2\pi C_{gs}}$$

• For the bulk-driven MOSFET,  $f_T$  is given by

$$f_{T,bulk-driven} = \frac{g_{mb}}{2\pi (C_{bs} + C_{bsub})} = \frac{\eta g_m}{2\pi (C_{bs} + C_{bsub})}$$

where  $\eta$  is the ratio of  $g_{mb}$  to  $g_m$  and typically has a value in the range of 0.2 to 0.4.

## Disadvantages of Bulk-Driven MOS Transistors ( cont'd)

• For typical saturated strong inversion MOSFET operation, the following approximation stands,

$$f_{T,bulk-driven} \approx \frac{\eta}{3.8} f_{T,gate-driven}$$

• Another disadvantage of bulk-driven MOSFETs is that the polarity of the bulk-driven MOSFETs is process related. For an P well CMOS process, we only have N channel bulk-driven MOSFETs available, and for N well CMOS process, only P channel MOSFETs. This limits its application. We can not use bulk-driven MOS transistors in some circuit structures which requires both N and P MOSFETs.

## Disadvantages of Bulk-Driven MOS Transistors ( cont'd)

- MOS transistors can be laid out in the same well, thus their characteristics will match better. Bulk driven transistors are in differential wells, it is inconvenient to design some circuits which require tight matching between transistors. For bulk-driven MOSFETs, it is not easy to utilize some layout techniques such as interdigitized and common centroid layout to make good matching.

- Potentials to turn on the parasitic BJT transistors which may result in latch-up problem

- The equivalent noise of a bulk-driven MOS amplifier is larger than a conventional gate-driven MOS amplifier.

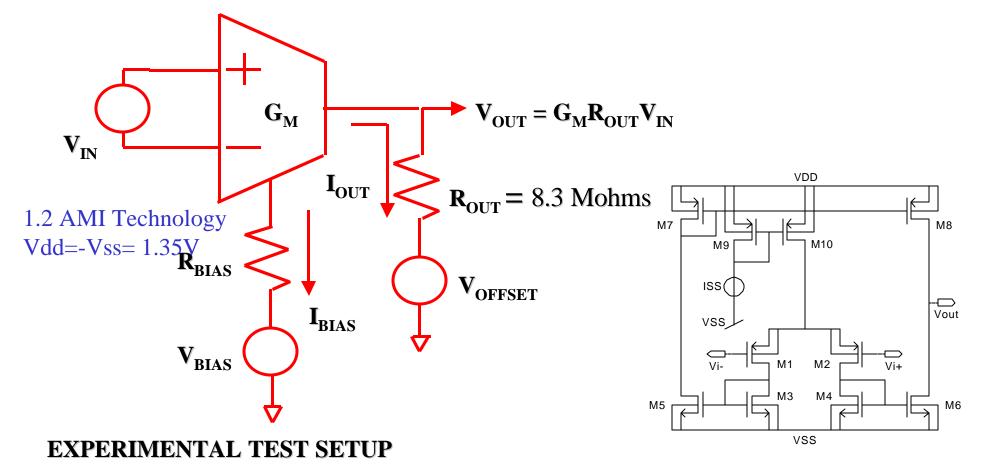

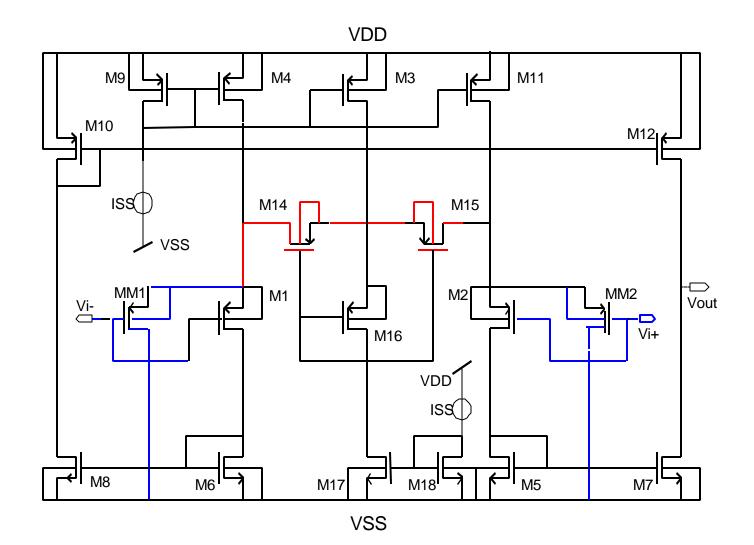

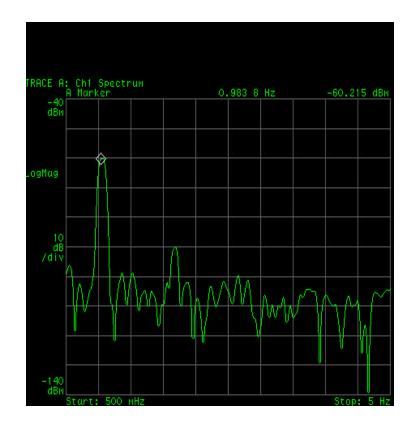

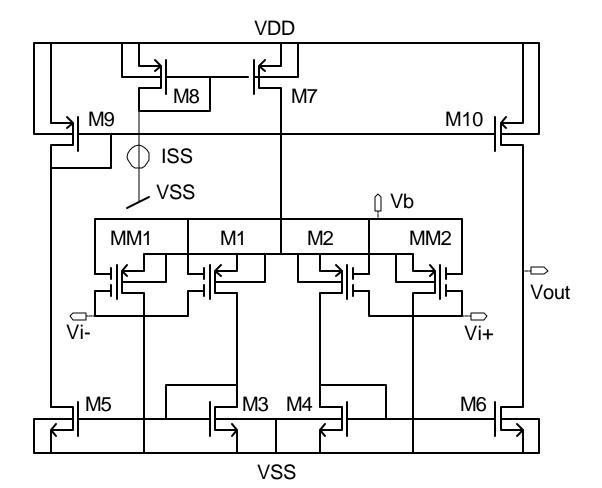

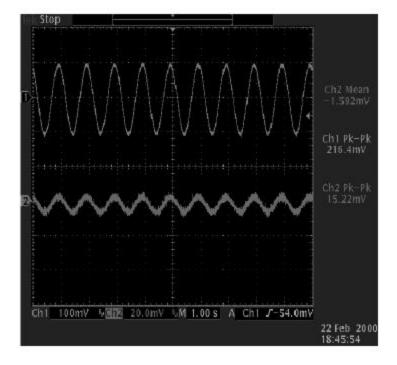

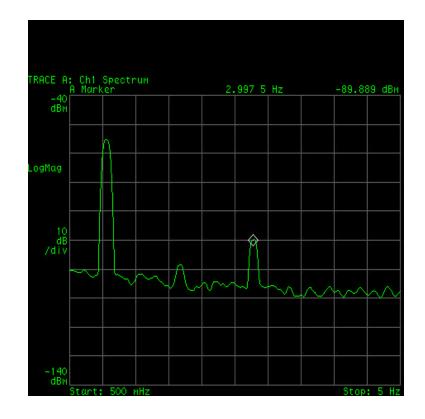

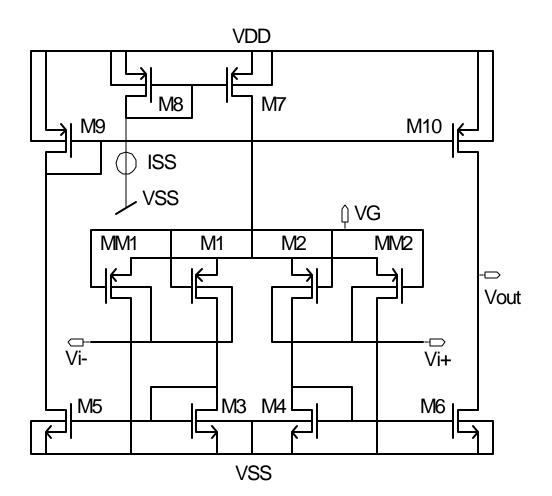

Example of OTAs using different approaches: Conventional, Current Divider-Source Degeneration (CD-SD), Floating Gate, and Bulk Driven

**DESIGN A - REFERENCE OTA**

## **DESIGN A - REFERENCE OTA**

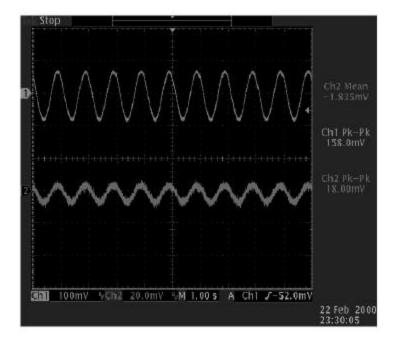

Input Ch1 160mVpp @ 1 Hz Output Ch2 18mVpp

#### THD ~ -28dBm ~ 3.9% @160mVpp, 1Hz

# **DESIGN B - CURRENT DIVISION OTA and Source Degeneration**

## **DESIGN B - CURRENT DIVISION and SD OTA**

#### Input Ch1 214mVpp @ 1 Hz Output Ch2 16mVpp

THD ~ -30dBm ~ 3.2% @214mVpp, 1Hz

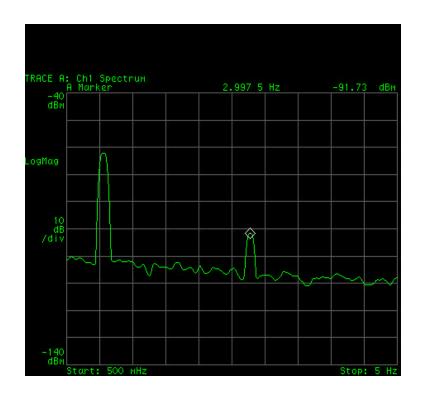

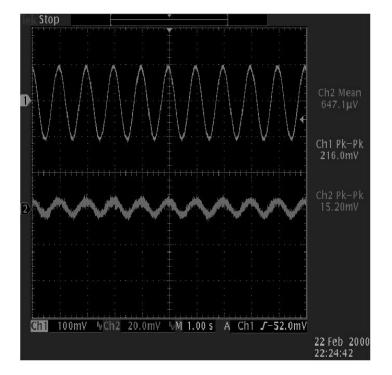

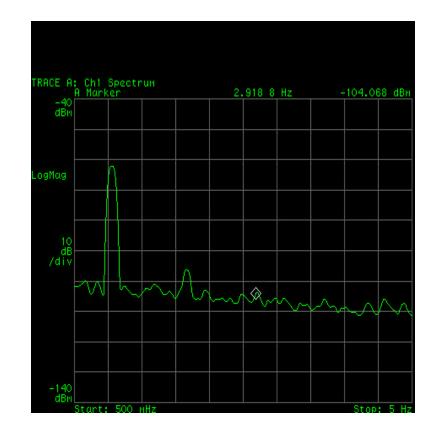

# **DESIGN C - FLOATING GATE OTA, plus SD and CD**

# **DESIGN C - FLOATING GATE OTA**

Input Ch1 214mVpp @ 1 Hz Output Ch2 15.2mVpp

THD ~ -34dBm ~ 2% @214mVpp, 1Hz

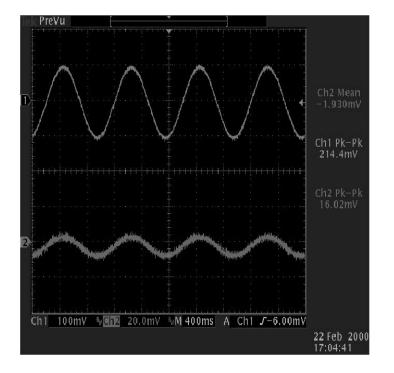

### **DESIGN D - BULK DRIVEN OTA, PLUS CD AND SD**

## DESIGN D - BULK DRIVEN OTA

Input Ch1 214mVpp @ 1 Hz Output Ch2 15.2mVpp

THD ~ -39dBm ~ 1.1% @214mVpp, 1Hz

### **SIMULATION VS EXPERIMENTAL RESULTS**

### 1.2 micron CMOS Technology

| SIMULATED RESULTS      |       |       |        | EXPERIMENTAL RESULTS |         |         |         |         |

|------------------------|-------|-------|--------|----------------------|---------|---------|---------|---------|

| <b>PAR \ DES</b>       | Α     | B     | С      | D                    | Α       | B       | С       | D       |

| $G_{M}(nA/V)$          | 11.6  | 11.55 | 11.51  | 11.24                | 10.5    | 9.3     | 8.7     | 8.8     |

| Δφ @ 1Hz               | 0.1   | 0.098 | 0.047  | 0.025                | <1      | <1      | <1      | <1      |

| (°)                    |       |       |        |                      |         |         |         |         |

| Offset (mV)            | 0.07  | 0.027 | -0.086 | 0.045                | -1.8    | -1.9    | -1.5    | 0.647   |

| THD (%)                | 1@162 | 1@240 | 1@330  | 1@900                | 3.9@160 | 5.6@242 | 3.2@330 | 5.9@900 |

|                        | mVpp  | mVpp  | mVpp   | mVpp                 | mVpp    | mVpp    | mVpp    | mVpp    |

| THD (%) @              | ) _   | -     | -      | -                    | 3.9     | 3.2     | 2       | 1.1     |

| 214mVpp                |       |       |        |                      |         |         |         |         |

| I <sub>BIAS</sub> (nA) | 2     | 100   | 200    | 500                  | 4       | 120     | 230     | 560     |

| $V_{DD} =  V_{SS} $    | 1.35  | 1.35  | 1.35   | 1.35                 | 1.35    | 1.35    | 1.35    | 1.35    |

| (V)                    |       |       |        |                      |         |         |         |         |

| BIAS (V)               | N/A   | N/A   | -1.35  | -1.35                | N/A     | N/A     | -1.35   | -1.35   |

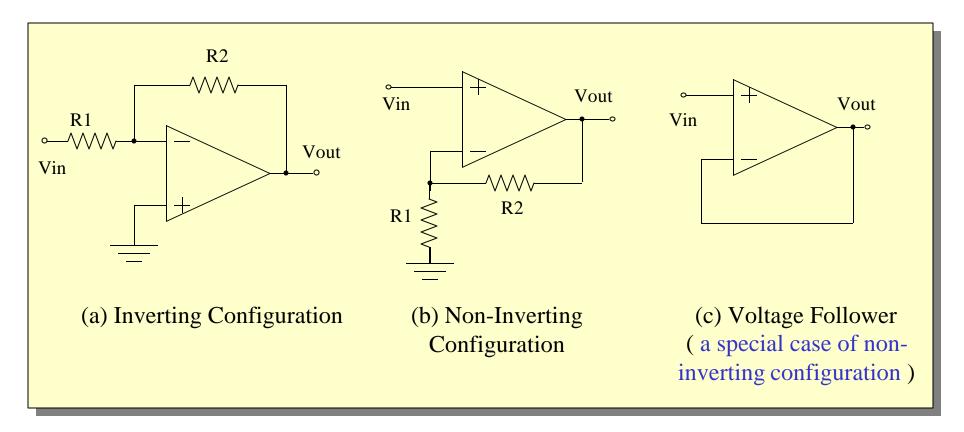

# **Rail-to-Rail Op Amps**

- There are two basic configurations for Op Amp applications:

- (a) inverting configuration, and,

- (b) non-inverting configuration.

# Why Rail-to-Rail Differential Input Stage?

• The input and output swings of inverting and non-inverting configurations

| Configuration    | Input common mode | Output voltage swing |  |

|------------------|-------------------|----------------------|--|

|                  | voltage swing     |                      |  |

| Inverting        | ≈0                | Rail-to-rail         |  |

| Non-inverting    | R1/(R1+R2) * Vsup | Rail-to-rail         |  |

| Voltage follower | Rail-to-rail      | Rail-to-rail         |  |

From the table, we see that for inverting configuration, rail-to-rail input common mode range is not needed. But for non-inverting configuration, some input common mode voltage swing is required, especially for a voltage follower which usually works as an output buffer, we need a rail-to-rail input common mode voltage range! To make an Op Amp work under any circumstance, a differential input with rail-to-rail common mode range is needed.

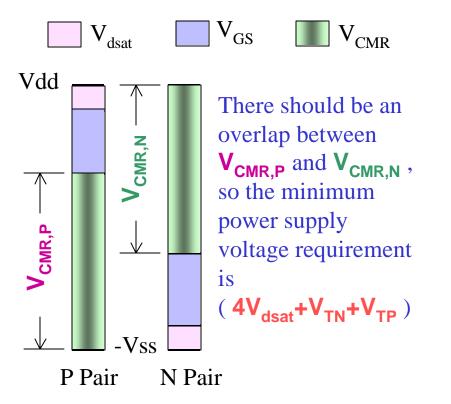

# How to Obtain a Rail-to-Rail Input Common Mode Range?

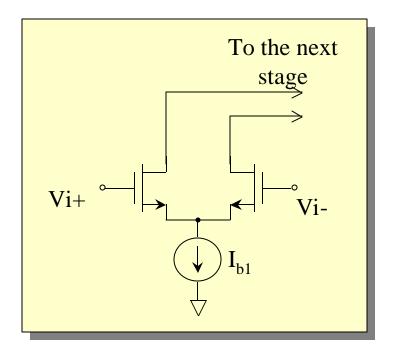

• We know that usually the input stage of an op amp consists of a differential pair. There are two types of differential pairs.

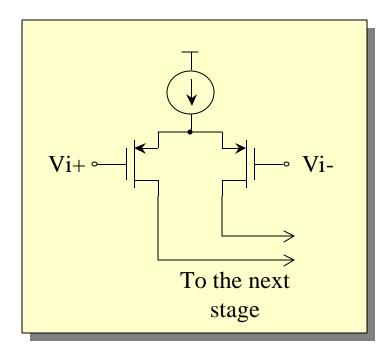

(a) P-type differential input stage

(b) N-type differential input stage

- First, let us observe how a differential pair works with different input common mode voltage

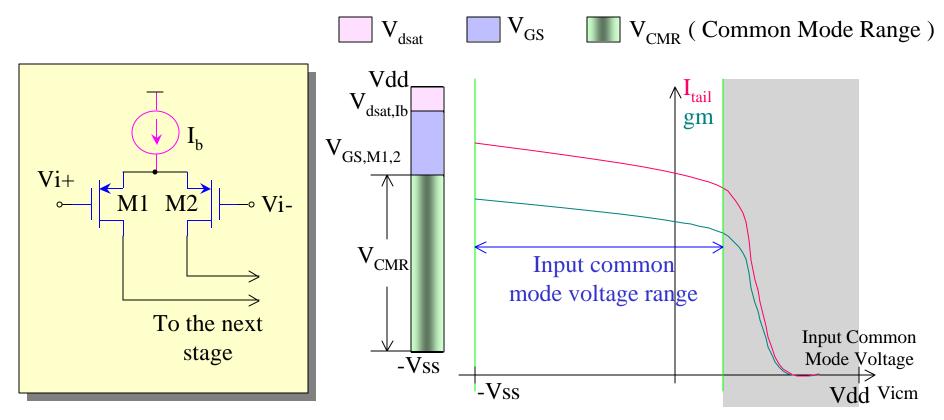

- P-type input differential pair

Where  $V_{GS} = V_{dsat} + V_T$

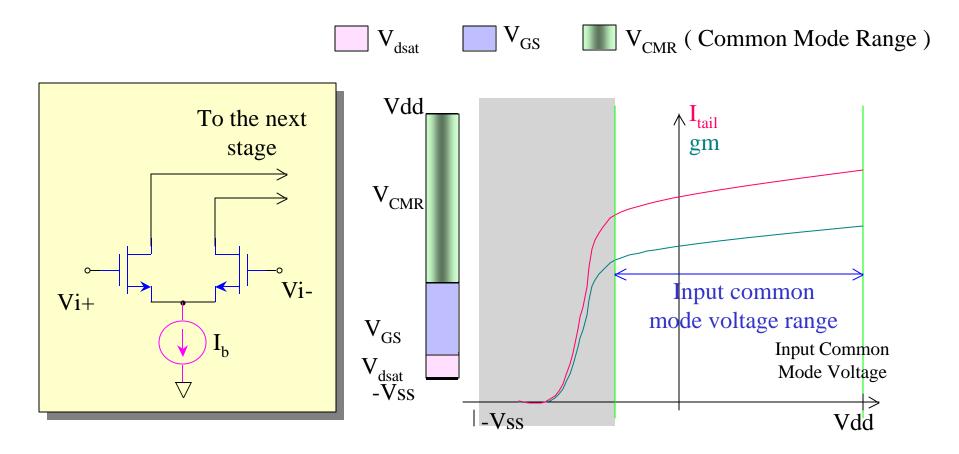

- N-type differential input stage

# Again, how to Obtain a Rail-to-Rail Input Common Mode Range?

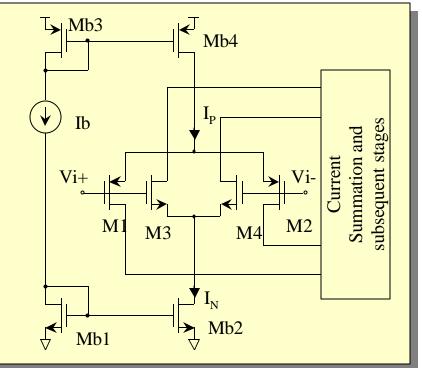

• Why not connect these two pairs in parallel and try to get a full rail-to-rail range?

Simple N-P complementary input stage Almost all of the rail-to-rail input stages are doing in this way by some variations! But how well does it work?

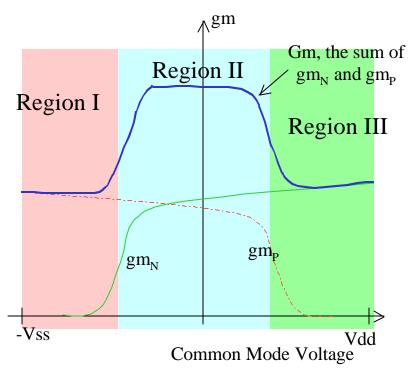

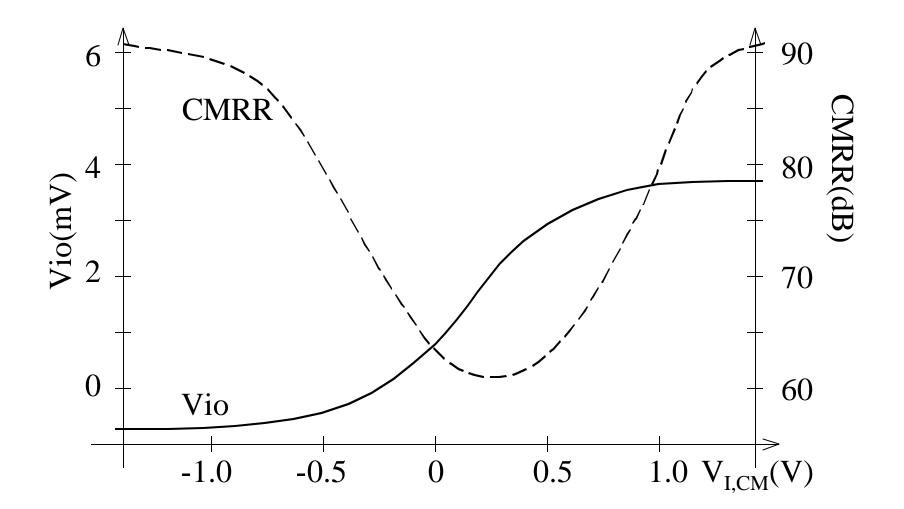

# Observations on transconductance performance for the entire region.-

• Transconductance vs. Vicm

The total transconductance of the input stage varies from gm to 2gm, the variation is **100%** !

• If

$$K = \frac{1}{2} KP_N (\frac{W}{L})_N = \frac{1}{2} KP_P (\frac{W}{L})_P$$

and

$$I_N = I_P = I_{TAIL}$$

then gm<sub>N</sub>=gm<sub>P</sub>=gm= $\sqrt{2KI_{TAIL}}$ .

- Region I. When Vicm is close to the negative rail, only Pchannel pair operates. The N channel pair is off because its  $V_{GS}$  is less than  $V_T$ . The total transconductance of the differential pair is given by  $gm_T = gm_P = gm$ .

- Region II. When Vicm is in the middle range, both of the P and N pairs operate. The total transconductance is given by  $gm_T = gm_N + gm_P = 2gm$ .

Region III. When Vicm is close to the positive rail, only Nchannel pair operates. The total transconductance is given by  $gm_T = gm_N = gm$ . How does the CMRR varies with the input common-mode signal ?

### Rail-to-Rail Techniques: Summary and Comparison

| Case | Principle                                                                            | $\Delta gm$                                                                                                 | Slew Rate                  | CMRR                                          | Advantage                                                    | Limitations                                                                                                                                                                                                                                             |

|------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | $I_N + I_P = const [1][2][6]$                                                        | N/A for weak<br>inversion<br>40% if in strong<br>inversion                                                  | Constant                   | 56dB@10Hz,<br>52dB@100KHz,<br>measured in [2] | Small gm<br>variation (6%) in<br>weak inversion<br>operation | Only work well in weak inversion, can<br>not used in high speed application                                                                                                                                                                             |

| 2    | $\sqrt{I_N} + \sqrt{I_P} = const [3]$ [16]                                           | -12% +6% (<br>simulated in this<br>presentation )                                                           | $\sqrt{2}$ times variation | 80 dB / 53 dB<br>( measured in [3] )          |                                                              | Depends on quadratic characteristics of<br>MOSFETs, which is not exactly<br>followed for short channel transistors in<br>sub-micron processes                                                                                                           |

| 3    | 4 times I <sub>N</sub> or I <sub>P</sub> when<br>only one pair operates<br>[3][4][6] | +15% systematic gm<br>variation                                                                             | 2 times variation          | 70dB / 43 dB<br>( measured in [4] )           | Somewhat simple                                              | <ol> <li>Same with case 2, but we can<br/>change 4 to other numbers to have<br/>smaller gm variation for short<br/>channel transistors</li> <li>Systematic gm deviation of 15%<br/>even for ideal MOSFETs with<br/>quadratic characteristics</li> </ol> |

| 4    | Current switch, backup<br>pairs [5]                                                  | +20% systematic gm<br>variation                                                                             | Constant                   | N/A                                           | Constant slew rate                                           | Systematic gm deviation of 20% even<br>for ideal MOSFETs with quadratic<br>characteristics                                                                                                                                                              |

| 5    | 6-pair structure, back<br>pairs [7]                                                  | +20% systematic gm<br>variation ( analytical<br>),<br>±10% ( measured in<br>[7])                            | Constant                   | N/A                                           | Constant slew rate                                           | Same with Case 4                                                                                                                                                                                                                                        |

| 6    | Max/min selection [8][9]                                                             | 7% (simulated [9])<br>5% (strong<br>inversion, measured<br>[8])<br>20% (weak<br>inversion, measured<br>[8]) | Constant                   | N/A                                           |                                                              | Somewhat complex                                                                                                                                                                                                                                        |

| 7    | Electronic zener [10]                                                                | 8% ( measured )                                                                                             |                            | 80 dB / 43 dB<br>( measured in [10] )         |                                                              | Same with Case 2                                                                                                                                                                                                                                        |

| 8    | Level shift [11]                                                                     | <sup>±</sup> 4% after tuning<br>13% before tuning<br>( measured )                                           |                            | ≥80 dB ( DC )<br>( measured in [11] )         | Simple                                                       | Gm variation sensitive to $V_T$ variation<br>and power supply voltage change                                                                                                                                                                            |

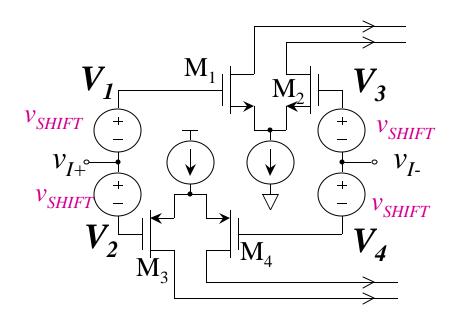

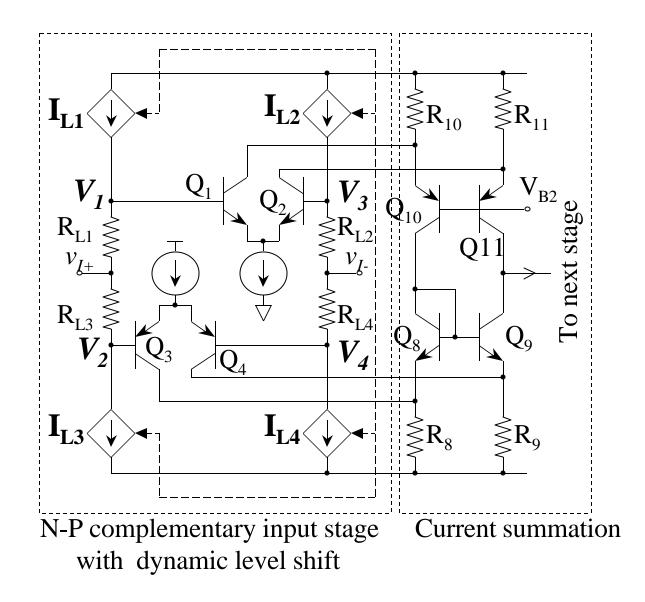

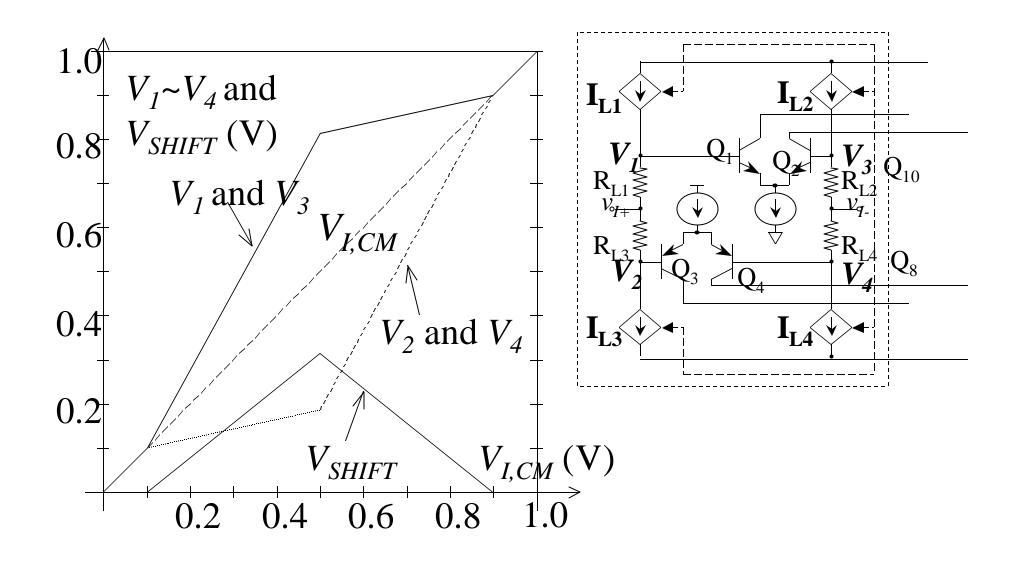

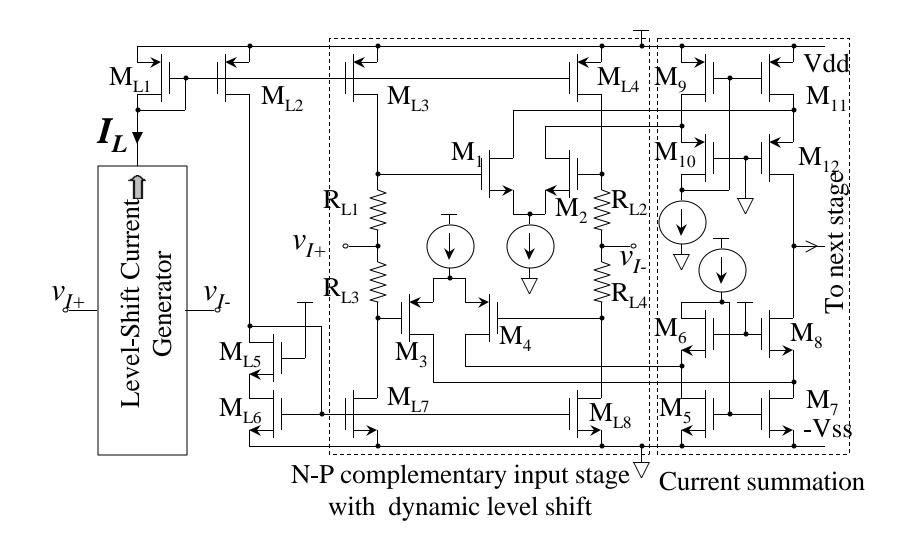

Another Potential Solutions for Rail-to-Rail Amplifiers

One more Rail-to-Rail Op Amp Technique

By using dynamic level shift, the rail-to-rail Amplifier can be obtained.

# References

- J. H. Huijsing, and D. Linebarger, "Low voltage operational amplifier with rail-torail input and output stages," *IEEE Journal of Solid-State Circuits*, vol. SC-20, no. 6, pp. 1144-1150, December 1985

- [2] W.-C. S. Wu, W. J. Helms, J. A. Kuhn, and B. E. Byrkett, "Digital-compatible high-performance operational amplifier with rail-to-rail input and output ranges," *IEEE Journal of Solid-State Circuits*, vol. 29, no. 1, pp. 63-66, January 1994

- [3] R. Hogervorst, R. J. Wiegerink, P. A. L. de Jong, J. Fonderie, R. F. Wassenaar, and J. H. Huijsing, "CMOS low-voltage operational amplifiers with constant-gm rail-*IEEE Proc. ISCAS* 1992, pp. 2876-2879

- [4] R. Hogervost, J. P. Tero, R. G. H. Eschauzier and J. H. Huijsing, "A compact power-efficient 3-V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries," *IEEE Journal of Solid-State Circuits*, vol. 29, no. 12, pp. 1505-1513, December 1994

- [5] R. Hogervorst, S. M. Safai, and J. H. Huijsing, "A programmable 3-V CMOS railto-rail opamp with gain boosting for driving heavy loads," *IEEE Proc. ISCAS 1995*, pp. 1544-1547

- [6] J. H. Huijsing, R. Hogervorst, and K.-J. de Langen, "Low-power low-voltage VLSI operational amplifier cells," *IEEE Trans. Circuits and Systems-I*, vol. 42. no. 11, pp. 841-852, November 1995

# References ( cont'd )

- [7] W. Redman-White, "A high bandwidth constant *gm*, and slew-rate rail-to-rail CMOS input circuit and its application to analog cell for low voltage VLSI systems," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 5, pp. 701-712, May 1997

- [8] C. Hwang, A. Motamed, and M. Ismail, "LV opamp with programmable rail-torail constant-gm," *IEEE Proc. ISCAS 1997*, pp. 1988-1959

- C. Hwang, A. Motamed, and M. Ismail, "Universal constant-gm input-stage architecture for low-voltage op amps," *IEEE Trans. Circuits and Systems-I*, vol. 42. no. 11, pp. 886-895, November 1995

- [10] R. Hogervost, J. P. Tero, and J. H. Huijsing, "Compact CMOS constant-gm rail-torail input stage with gm-control by an electronic zener diode," *IEEE Journal of Solid-State Circuits*, vol. 31, no. 7, pp. 1035-1040, July 1996

- M. Wang, T. L. Mayhugh, Jr., S. H. K. Embabi, and E. Sánchez-Sinencio, "Constant-gm rail-to-rail CMOS op-amp input stage with overlapped transition *IEEE Journal of Solid-State Circuits*, vol. 34, no. 2, pp. 148-156, February 1999

- [12] G. Ferri and W. Sansen, "A rail-to-rail constant-gm low-voltage CMOS operational transconductance amplifier," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 10, pp. 1563-1567, October 1997

# References (cont'd)

IEEE Journal of Solid-State Circuits, vol. 35, no. 1, pp. 33-44, January 2000

#### Voltage Multistage Transconductance Amplifier Topologies For LV Power Supply.

- Good voltage gain can be obtained using cascode stages. But these stages are not amenable for LV power supply.

- Under LV conditions, high voltage can be obtained using cascade amplifiers. That is growing horizontally, rather than vertically.

- Direct Cascade of simple (inverting) stages gives the required voltage gain without control of poles and zeroes.

- Dynamic behavior for optimal performance requires feedback (and feedforward) circuits.

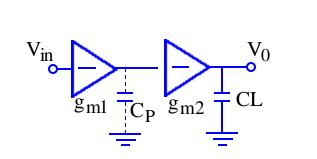

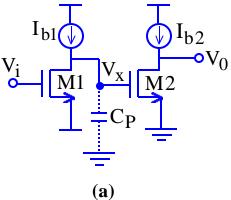

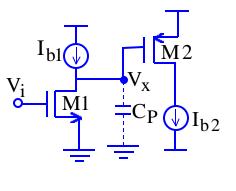

#### First Approach: Direct Cascade

Symbolic Representation

**(b)**

**Two Possible Implementations**

$$H(s) = \frac{V_0(s)}{V_{in}(s)} \approx \frac{+g_{m1}g_{m2}/C_pC_L}{1+s\left(\frac{C_L}{g_{02}} + \frac{C_p}{g_{01}}\right) + \frac{C_pC_L}{g_{01}g_{02}}s^2}$$

The poles are located at

$$\omega_{p_1} = \frac{g_{01}}{C_p}, \ \omega_{p_2} = \frac{g_{02}}{C_L}$$

$$H(o) = \frac{g_{m1}g_{m2}}{g_{01}g_{02}}$$

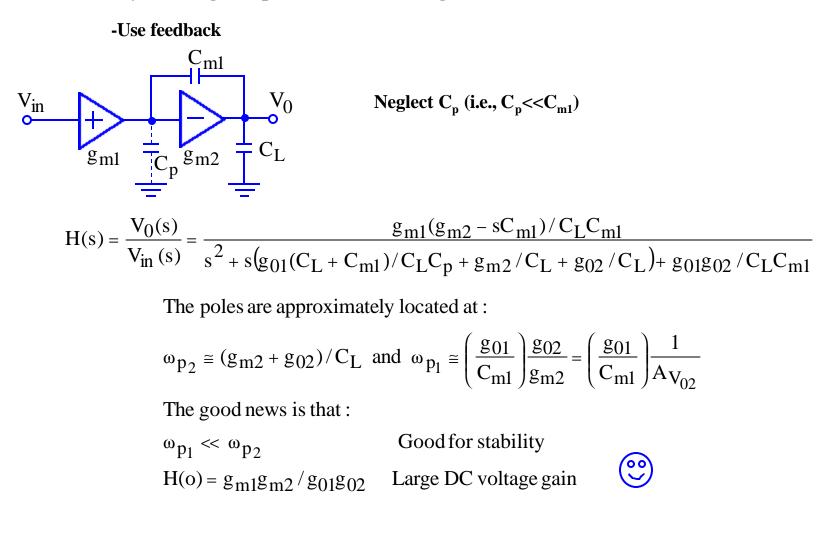

#### How do you bring one pole close to the origin?

The bad news is a zero at the RHP

$$\omega_{z_1} = \frac{g_{m2}}{C_{m1}}$$

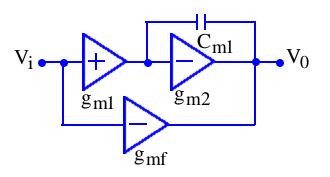

Now we will use a feedforward circuit to cancel the zero at the RHP.

This will impact the complexity and performance of the design. Recall that before applying the feedforward we had:

$$H(s) = \frac{V_{0}(s)}{V_{in}(s)} = \frac{g_{m1}(g_{m2} - sC_{m1})/C_{L}C_{m1}}{s^{2} + s(g_{01}(C_{L} + C_{m1})/C_{L}C_{p} + g_{m2}/C_{L} + g_{02}/C_{L}) + g_{01}g_{02}/C_{L}C_{m1}}$$

Now the corresponding H(s) becomes:

$$V_{in} = \frac{C_{m1}}{g_{m1}}$$

Now the corresponding H(s) becomes:

$$H(s) = \frac{-g_{m1}g_{m2}}{s^{2}C_{m1}C_{L} + sC_{m1}g_{m2} + g_{01}g_{02}}$$

$$H(s) = \frac{-g_{m1}g_{m2}}{s^{2}C_{m1}C_{L} + sC_{m1}g_{m2} + g_{01}g_{02}}$$

This can be extended to higher-order systems, let us consider first a third-order system.

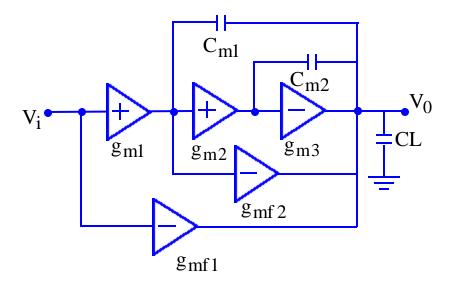

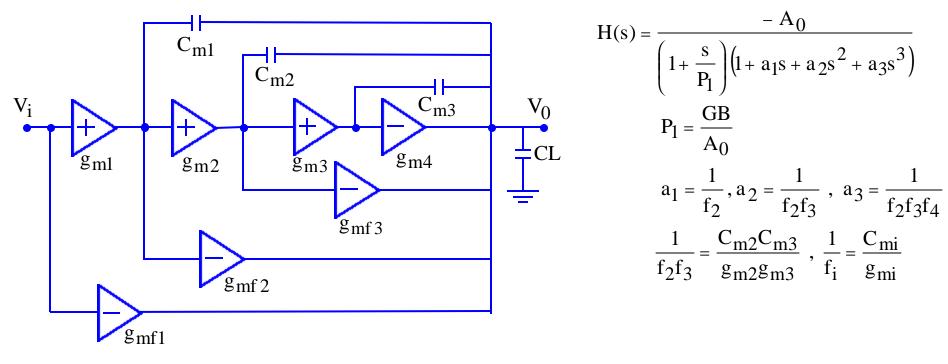

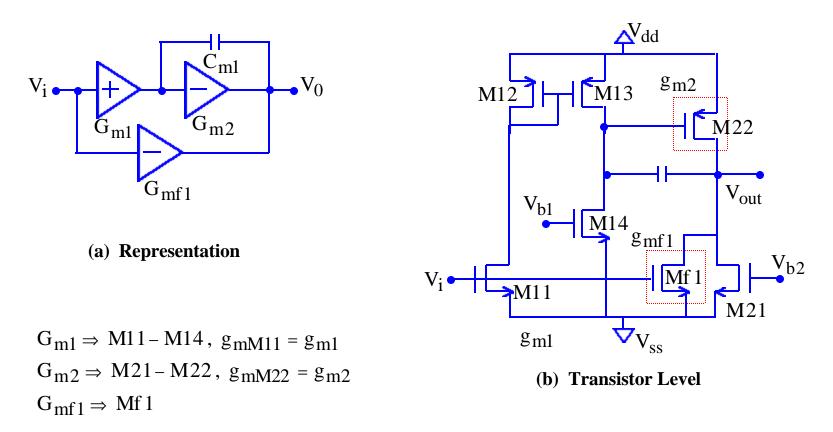

Nested G<sub>m</sub>-C Compensation Amplifier.

Three-stage amplifier topology with NGCC

$$H(s) = \frac{V_0(s)}{V_i(s)} = \frac{g_{m1}g_{m2}g_{m3} + sg_{m1}(g_{mf2} - g_{m2})C_{m2} + (g_{mf1} - g_{m1})C_{m1}C_{m2}}{g_{01}g_{02}g_{03} + sg_{m2}g_{m3}C_{m1} + s^2(g_{m3} + g_{mf2} - g_{m2})C_{m1}C_{m2} + s^3C_LC_{m1}C_{m2}}$$

By making

$$g_{mf1} = g_{m1}$$

and  $g_{mf2} = g_{m2}$ ,

$$H(s) = \frac{V_0(s)}{V_i(s)} = \frac{-g_{m1}g_{m2}g_{m3}}{g_{01}g_{02}g_{03} + sg_{m2}g_{m3}C_{m1} + s^2g_{m3}C_{m1}C_{m2} + s^3C_LC_{m1}C_{m2}}$$

Analog & Mixed-Signal Center (AMSC)

This H(s) can be written as

$$H(s) = \frac{-A_0}{\left(1 + s\frac{A_0}{f_1}\right) \left(1 + \frac{s}{f_2} + \frac{s^2}{f_2 f_3}\right)}$$

$$A_{0} = \frac{g_{m1}g_{m3}g_{m2}}{g_{01}g_{03}g_{02}} \text{ and } f_{1} = GB = \frac{g_{m1}}{C_{m1}}$$

$$f_{2} = \frac{g_{m2}}{C_{m2}}, f_{2}f_{3} = \frac{g_{m2}g_{m3}}{C_{m2}C_{L}}; f_{i} = \frac{g_{mi}}{C_{mi}}$$

Note that the dominant pole is located at

$$P_{1} = \frac{f_{1}}{A_{0}} = \frac{\frac{g_{m1}}{C_{m1}}}{\frac{g_{m1}g_{m2}g_{m3}}{g_{01}g_{02}g_{03}}} = \frac{g_{01}g_{02}g_{03}}{g_{m2}g_{m3}C_{m1}} = \left(\frac{g_{01}}{C_{m1}}\right)\frac{1}{A_{V0_{2}}A_{V0_{3}}}$$

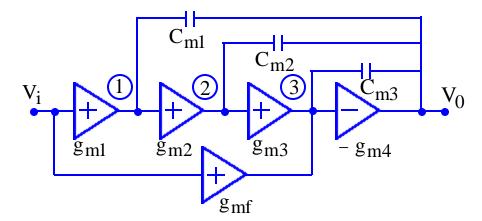

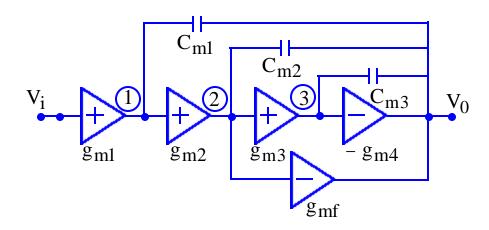

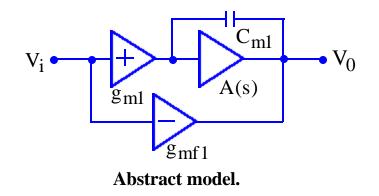

#### Multipath Nested Miller Compensation Technology Potential Feedforward Schemes: An Amplifier Topologies Re-Visit.

(a) Multipath nested miller compensation topology. FF

(b) An abstract model for the amplifier proposed by Castello, et.al.

(c ) The amplifier with multipath miller zero cancellation.

#### Let Us Now Compare Several Four-Order Topologies

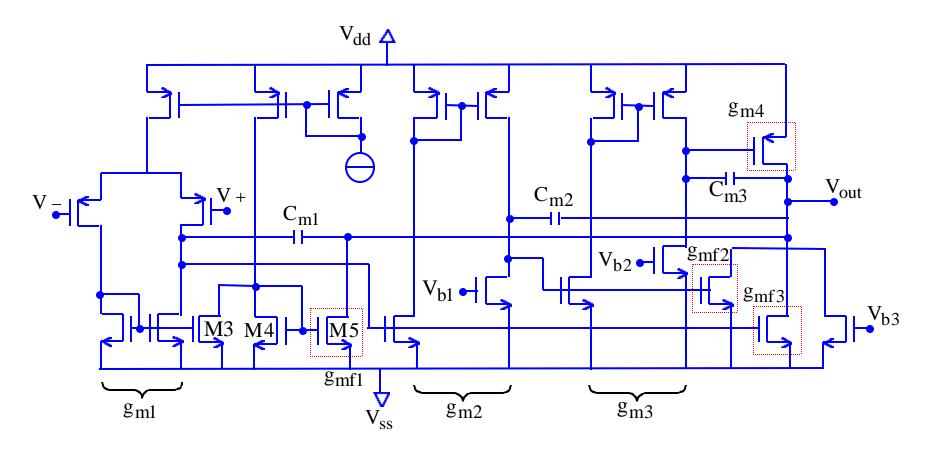

Four stage amplifier topology with NGCC (Fan You et al)

$$\begin{array}{l} f_1 < f_2 < f_3 \leq f_4 \ , \ f_1 = GB \\ f_4 > \frac{f_2}{1 - f_2 \, / \, f_3} \end{array}$$

$$P = (V_{DD} - V_{SS})I_n \left[ 1 + \sum_{i=1}^{n-1} \frac{\alpha_i f_i}{f_n} \right], \ \alpha_i = \frac{C_{mi}}{C_L}, \ \alpha_i f_i = \frac{g_{mi}}{C_L}$$

$\boldsymbol{I}_n$  and  $\boldsymbol{f}_n$  are current and frequency normalization factors, respectively.

#### **Comparison of Several Topologies.**

$$\frac{V_0(s)}{V_i(s)} = -A_0 \frac{1 - b_1 s - b_2 s^2 - b_3 s^3}{(1 + s/P_1)(1 + a_1 s + a_2 s^2 + a_3 s^3)} , \qquad k_i = \frac{g_{mi}}{g_{oi}}, i = 1,3 \text{ and } f_i = \frac{g_{mi}}{C_{mi}}$$

Where

$$A_0 = k_1 k_2 k_3 k_4$$

,  $P_1 = \frac{f_1}{A_0} = \frac{GB}{A_0}$

#### Comparison of Polynomial Coefficients for Four Stage NMC and NGCC Amplifier.

| P <sub>h</sub> (s) | a <sub>1</sub>                                             | <b>a</b> <sub>2</sub>                                                       | a <sub>3</sub>                                                                                      |           |

|--------------------|------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|

| NMC                | $\frac{(g_{m 4}C_{m 2} - g_{m 2}C_{m 3})}{g_{m 2}g_{m 4}}$ | $\frac{(g_{m 4} - g_{m 2} - g_{m 3})C_{m 2}C_{m 3}}{g_{m 2}g_{m 3}g_{m 4}}$ | $\frac{C_{m2}C_{m3}C_{L}}{g_{m2}g_{m3}g_{m4}}$                                                      | ← Complex |

| NGCC               | $\frac{C_{m 2}}{g_{m 2}}$                                  | $\frac{C_{m2}C_{m3}}{g_{m2}g_{m3}}$                                         | <u>C<sub>m2</sub>C<sub>m3</sub>C<sub>L</sub></u><br>g <sub>m2</sub> g <sub>m3</sub> g <sub>m4</sub> | < Simple  |

|                    |                                                            |                                                                             |                                                                                                     | 1         |

| Z(s)               | b <sub>1</sub>                                             | b <sub>2</sub>                                                              | b <sub>3</sub>                                                                                      |           |

| NMC                | $\frac{C_{m3}}{g_{m4}}$                                    | $\frac{C_{m2}C_{m3}}{g_{m3}g_{m4}}$                                         | $\frac{C_{m1}C_{m2}C_{m3}}{g_{m2}g_{m3}g_{m4}}$                                                     |           |

| NGCC               | 0                                                          | 0                                                                           | 0                                                                                                   |           |

Design

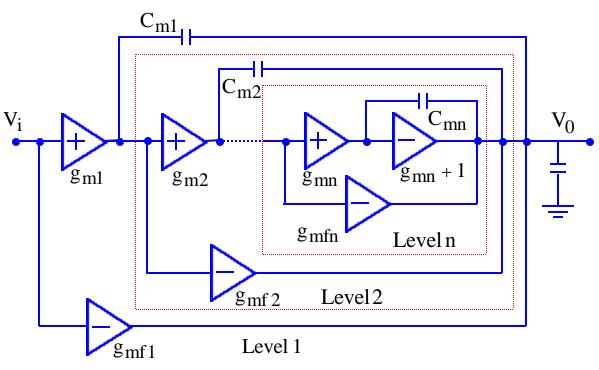

Nested G<sub>m</sub>-C Compensation (NGCC) N<sup>th</sup>-Order

Conceptual multistage amplifier topology with NGCC.

How to Implement a Positive G<sub>m</sub>?

- If  $G_{m2} > G_{mf1}$ , M22 current > Mf1 current, then add M21 to provide additional current.

- If  $G_{m2} > G_{mf1}$ , Remove M21 and add a PMOS transistor in parallel to M22.

#### **Design Example of a Four-Stage Amplifier**

Four stage operational amplifier with NGCC topology

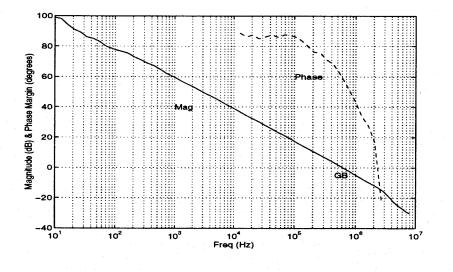

#### Measured Performance of the 4-Stage NGCC Op Amp.

| Power Consumption | 0.68mW                            | 1.40mW              |

|-------------------|-----------------------------------|---------------------|

| DC Gain           | ≈ 100dB                           | ≈ 100dB             |

| Gain Bandwidth    | 610kHz                            | 1.0MHz              |

| Phase Margin      | $60^{\circ}$                      | 58°                 |

| Input Offset      | 5.2mV                             | 5.2mV               |

| Slew Rate         | $2.5V/\mu S$                      | 5.0V                |

| Power Supply      | $\pm 1.0 V$                       | $\pm 1.0 V$         |

| Load Condition    | $10 \mathrm{k}\Omega$ // $20  pF$ | 10k0//20pF          |

| Area              | 0.22mm <sup>2</sup>               | 0.22mm <sup>2</sup> |

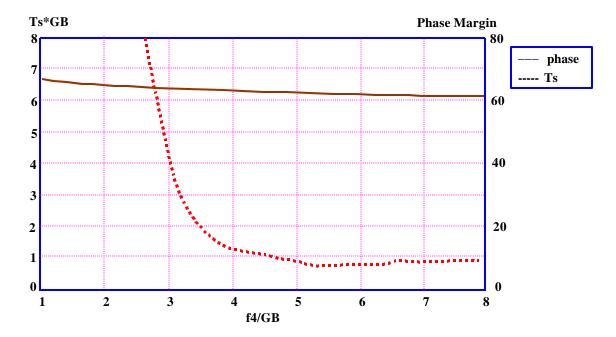

#### What is the effect of f<sub>4</sub>/GB?

#### How far should one push f<sub>4</sub>?

The phase margin and normalized settling time (TsGB) of an NGCC amplifier vs.  $f_4/GB$ .

• Trade-off between phase margin versus setting time.

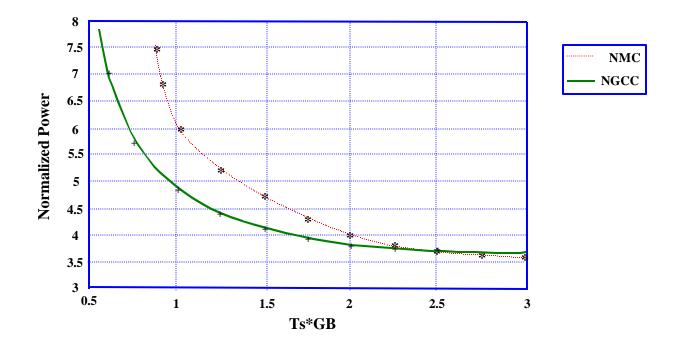

#### How do the Two Topologies Compare for Power Consumption?

The normalized power consumption of the NGCC and the NMC amplifiers as a function of the normalized settling time.

#### More Experimental Results.

Measured frequency response of 4-stage NGCC amplifier

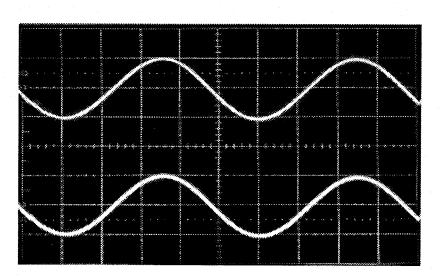

Measured 1.0Vp-p 100 KHz sin-wave at input and output nodes of a unity follower.

Analog & Mixed-Signal Center (AMSC)

### References

S. Pernici, "A CMOS Low-Distortion Fully Differential Power Amplifier with Double Nested Miller Compensation," *IEEE J. Solid-State Circuits*, Vol. 28, No. 7, pp. 758-763, July 1993.

F. You, S.H.K. Embabi and E. Sánchez-Sinencio, "Multistage Amplifier Topologies with Nested G<sub>m</sub>-C Compensation," *IEEE J. of Solid-State Circuits*, Vol. 32, No. 12, pp. 2000-2011, December 1997.

K.N. Leung, P.K. T. Mok, W.-H. Ki, and J. K. O. Sin, "Three-Stage Large Capacitive Load Amplifier with Damping Factor-Control Frequency Compensation, "*IEEE J. of Solid-State Circuits*, Vol. 35, No. 2, pp. 221-230, February 2000

S. Yan and E. Sánchez-Sinencio, Low Voltage Analog Circuit Design Techniques: A Tutorial, *IEICE Trans. Fundamentals*, Vol. E83-A, No. 2 February 2000

E. Sánchez-Sinencio and Andreas G. Andreou, Eds. "Low-Voltage/Low-Power Integrated Circuits and Systems ", IEEE Press, Piscataway, NJ 1999

A. Rodriguez-Vazquez and E. Sánchez-Sinencio, Eds., Special Issue on Low-Voltage and Low-Power Analog and Mixed-Signal Circuits and Systems, *IEEE Trans. on Circuits and Systems I*, vol. 42, No. 11, November 1995

Edgar

oe

### Conclusions

- Low power supply and smaller size technologies require new analog circuit techniques

- Power Consumption and area are critical specifications in portable equipment, clever design methodologies are needed.

# THANK YOU