# Texas A&M University Department of Electrical and Computer Engineering

## ECEN 474/704 - (Analog) VLSI Circuit Design

Fall 2016

### Exam #1

Instructor: Sam Palermo

- Please write your name in the space provided below

- Please verify that there are pages in your exam

- You may use one double-sided page of notes and equations for the exam

- Good Luck!

| Problem | Score | Max Score |  |

|---------|-------|-----------|--|

| 1       |       | 40        |  |

| 2       |       | 40        |  |

| 3       |       | 20        |  |

| Total   |       | 100       |  |

| Name: | SAM | PALERMO |  |  |

|-------|-----|---------|--|--|

| UIN:  |     |         |  |  |

#### Problem 1 (40 points)

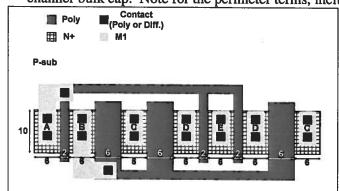

For the layout below, assume that all the commonly labeled diffusion areas are connected with the appropriate metal layers. Assume that  $V_A=2V$ ,  $V_B=1.2V$ ,  $V_C=0V$ ,  $V_D=1.2V$ ,  $V_E=2V$ ,  $V_{T0}=0.7V$ ,  $\gamma=0$ , and that all Spice parameters are given (i.e.  $C_j$ ,  $C_{jsw}$ ,  $C_{jc}$ ,  $C_{ox}$ ,  $C_{ov}$ ). The dimensions are given in  $\mu m$ , with the poly gates having an  $L_D=0.1\mu m$ .

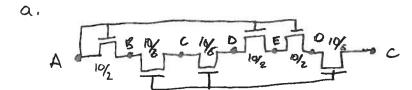

- a) Draw the equivalent circuit. Combine all parallel transistors and given the total width and length of the equivalent transistors.

- b) What region(s) are the transistors operating in?

- c) For node B only, give an expression and calculate the total gate cap.

- d) For node D only, give an expression and calculate the total junction cap, including the relevant channel-bulk cap. Note for the perimeter terms, include the sides underneath the gate.

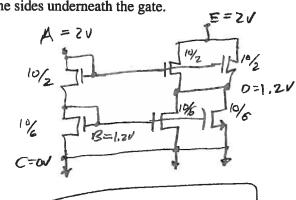

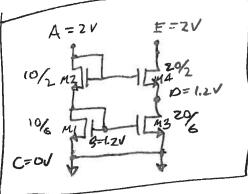

b.  $M(\Rightarrow) V_{GS} = V_{OS} = 1.2V > V_{T}$   $V_{OS} > V_{GS} - V_{T} \Rightarrow S_{Atwation}$   $M_{S} = V_{S} = 0.8V = V_{T}$   $M_{S} = V_{S} = 0.8V = V_{T}$

M2 = VGS = VGS - VT => Saturation

M4 sine as M2

d.  $C_{j0} = A_{0}C_{j} + P_{j}C_{js\omega} + C_{CBM4}$ =  $(G_{\mu\nu})(D_{\mu\nu})(2)C_{j} + (G_{\mu\nu}+D_{\mu\nu})(2)(2)C_{js\omega}$ +  $\frac{2}{3}(20\mu)(1.8\mu)C_{jc}$

(jo= 120,2C; + 64, Cjsw +24, 2C;c

$C, For (3B \Rightarrow MI = Sat \Rightarrow (9s + fg)$   $= \frac{2}{3}(10\mu)(5.8\mu)lox + 10\mu cov$   $= 38. 7\mu^{2}(ox + 10\mu)cov$   $M3 = Sat \Rightarrow (9s + (9d)$   $= \frac{2}{3}(20\mu)(5.8\mu)(ox + 20\mu)cov + 20\mu cov$

$= \frac{2}{3}(20\mu)(5.8\mu)(0x + 20\mu(0) + 20\mu(0)$   $= 77.3\mu^{2}(0x + 40\mu(0) + 50\mu(0)$

Total CgB = 116µ260x + 50µCov

#### Problem 2 (40 points)

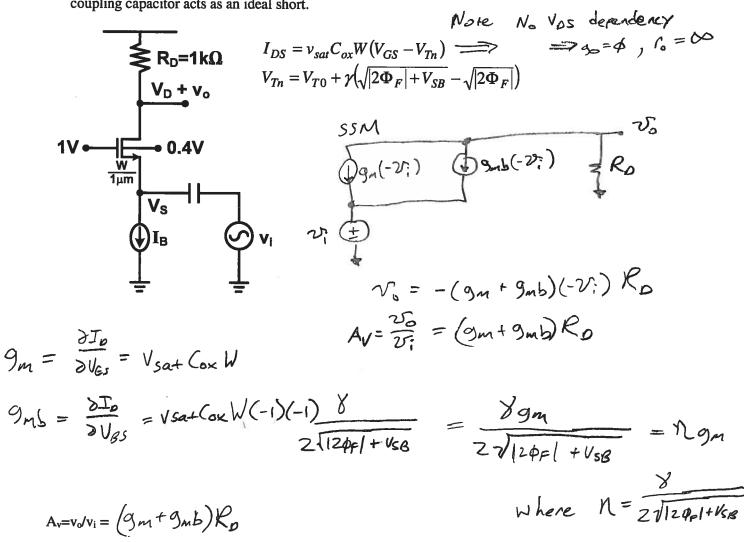

For the circuit shown below, the transistor is operating in a fully velocity saturated region where its DC drain current is given exactly by the given equation.

a. Draw the low-frequency small-signal model of the circuit (neglecting transistor capacitors) and give an expression for the small-signal voltage gain of the circuit,  $A_v=v_o/v_i$ , as a function of the relevant transistor conductances and the load resistor. Note, you can assume that the input AC-coupling capacitor acts as an ideal short.

b. Assume the following DC operating points for the drain and source voltages,  $V_{S,Q}=0.2V$  and  $V_{D,Q}=1V$ , and that  $v_{sat}C_{ox}=250\mu\text{A/}(V^*\mu\text{m})$ ,  $V_{T0}=0.7V$ ,  $\gamma=0.45V^{1/2}$ ,  $2\Phi_F=0.9V$ , and  $L_D=0.1\mu\text{m}$ . Calculate the necessary transistor width W for  $|A_V|=5V/V$ .

$$A_{V} = (9m + 9mb)R_{0} = (1 + N)g_{m}R_{0} = (1 + N)V_{saf}(0 \times WR_{0})$$

$$W = \frac{A_{V}}{(1 + N)V_{saf}(0 \times R_{0})} = \frac{5}{(1.269)(250 \frac{M^{A}}{V_{yan}})1kN} = 15.8 \mu m$$

$$W = \frac{6.45}{2\sqrt{1.09 - 0.2}} = 0.269$$

$$W = 0.269$$

Problem 3 (20 points)

#### a. Poly resistor design

Design and sketch a layout of a 500 $\Omega$  poly resistor. Assume that the poly R =60 $\Omega$ / $\Omega$ , each (1 $\mu$ m x 1 $\mu$ m) contact has resistance of 10 $\Omega$ , and fabrication tolerances limit the minimum unit resistor width W  $\geq$  3 $\mu$ m. Use at least 2 fingers in the resistor design. In the sketch clearly label the critical dimensions.

#### b. Poly resistor parasitic capacitance

The poly resistor has a parallel-plate parasitic capacitance to substrate of  $0.1 fF/\mu m^2$ . What is the total parasitic capacitance of the resistor? Include the contact area in the capacitance calculation and assume that the capacitance is only due to the parallel-plate effect, i.e. neglect any fringing capacitance.

Resistor Area is

$$(12.2\mu m + 2\mu m)(3\mu m)(2) = 86.4\mu m^2$$

$C_{parasitic} = (86.4\mu m^2)(0.147/\mu m^2) = 8.64f F$

#### c. N-well resistor design

Design and sketch a layout of a 500 $\Omega$  n-well resistor. Assume that the n-well R =2k $\Omega$ / $\square$ , each (1 $\mu$ m x 1 $\mu$ m) contact has resistance of 10 $\Omega$ , and fabrication tolerances limit the minimum unit resistor length L  $\geq$  6 $\mu$ m. Use at least 2 fingers in the resistor design. In the sketch clearly label the critical dimensions.

$$R_{tofal} = \left(\frac{2Rc}{n} + R_{\square} \frac{L}{W}\right) F$$

$$L = \left(\frac{R_{total}}{F} - \frac{2Rc}{n}\right) \frac{W}{R_{\square}}$$

$$Set F = 2, W = SO_{MM}, n = SO$$

$$L = \left(\frac{Soq}{2} - \frac{2(10)}{50}\right) \left(\frac{SO_{MM}}{2R}\right) = 6, 24_{MM}$$

$$SO_{MM} = \frac{SO_{MM}}{SO_{MM}}$$

$$SO_{MM} = \frac{SO_{MM}}{SO_{MM}}$$

#### d. N-well resistor parasitic capacitance

The n-well resistor has a parallel-plate parasitic capacitance to substrate of  $1 \text{FF}/\mu\text{m}^2$ . What is the total parasitic capacitance of the resistor? Include the contact area in the capacitance calculation and assume that the capacitance is only due to the parallel-plate effect, i.e. neglect any fringing capacitance.

Resistor Area is

$$(6.24 \mu m^2 3 \mu m)(50 \mu m)(2) = 824 \mu m^2$$

$$(parasitic = (824 \mu m^2)(1 + 1/m m^2) = 824 f F$$

e. If we have to use the  $500\Omega$  resistor for a high-frequency application, which design should we choose, the poly or n-well design? Why?

## **Scratch Paper**