### ECEN474/704: (Analog) VLSI Circuit Design Spring 2018

#### Lecture 6: Current Mirrors

Sam Palermo Analog & Mixed-Signal Center Texas A&M University

### Announcements & Agenda

- Reading

- Razavi Chapter 5

- Biasing in ICs

- Simple Current Mirror

- Cascode Current Mirror

- Low-Voltage Cascode Current Mirror

### **Current Source Properties**

- Finite output resistance degrades current source accuracy and amplifier gain

- Other important properties:

- Voltage headroom (compliance voltage)

- Accuracy

- Noise

# How Should We Bias Our Circuits?

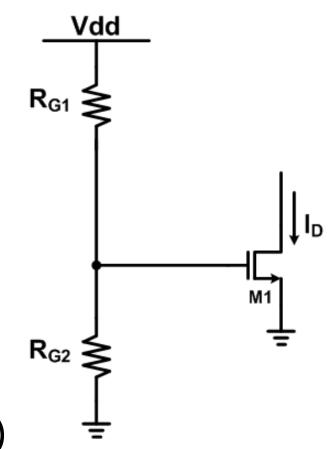

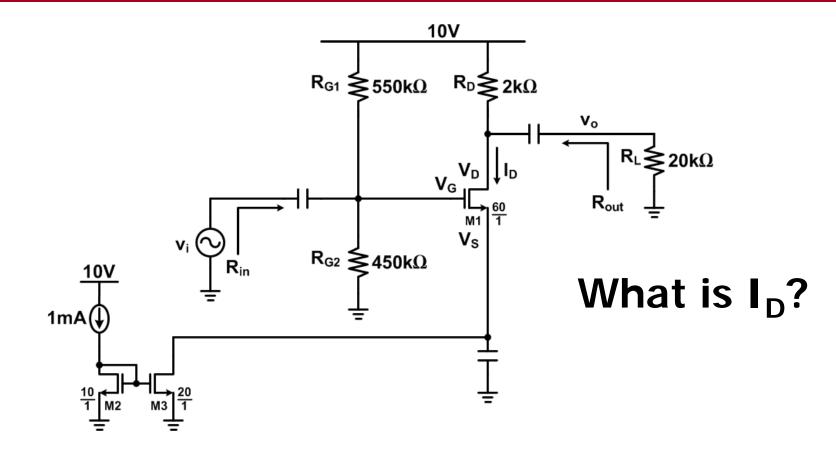

- Resistive Biasing

- Assuming saturation

$$I_{D} = \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{G} - V_{Tn})^{2}$$

$$= \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} \left( \frac{R_{G2}}{R_{G1} + R_{G2}} V dd - V_{Tn} \right)^{2}$$

- I<sub>D</sub> is sensitive to

- Supply (Vdd)

- Process ( $V_{Tn}$  and  $\mu_n C_{ox} W/L$ )

- Temperature ( $V_{Tn}$  and  $\mu_n$ )

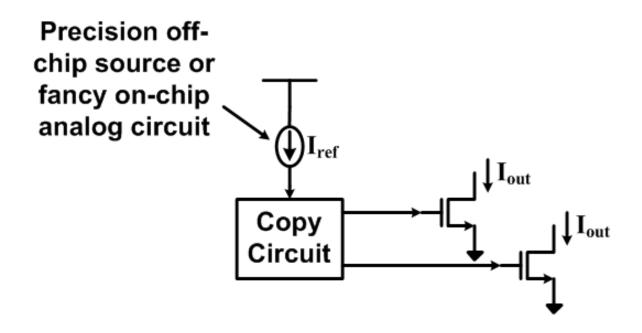

# IC Biasing

In IC design we often assume that we have one precise current source and we copy its value to our circuits

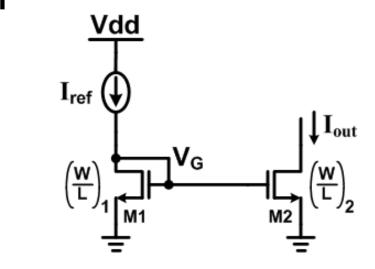

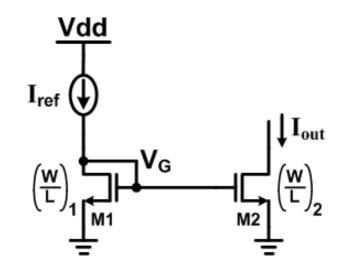

# Simple Current Mirror

- That copy circuit is a current mirror

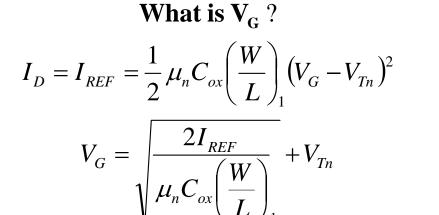

- Simple Current Mirror

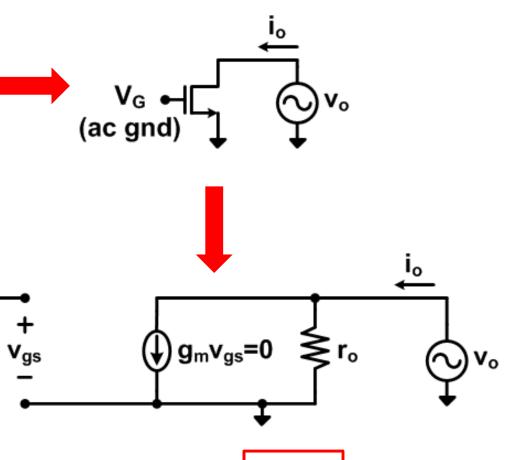

• If VG is applied to another transistor

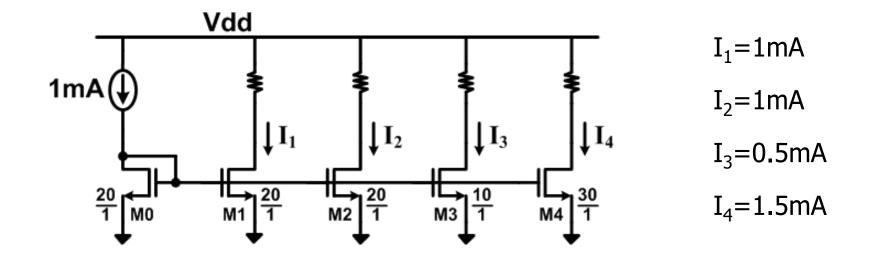

### Ideal Current Mirror Example

This bias scheme reduces sensitivity to process, voltage, and temperature variations

# CS Amplifier w/ Current Source

Need to insure that M3 remains in saturation

$$V_{s} = V_{G} - (V_{ov1} + V_{Tn}) = \left(\frac{R_{G2}}{R_{G1} + R_{G2}}\right) V dd - \left(\sqrt{\frac{2I_{D}}{\mu_{n}C_{ox}}\left(\frac{W}{L}\right)_{1}} + V_{Tn}\right)$$

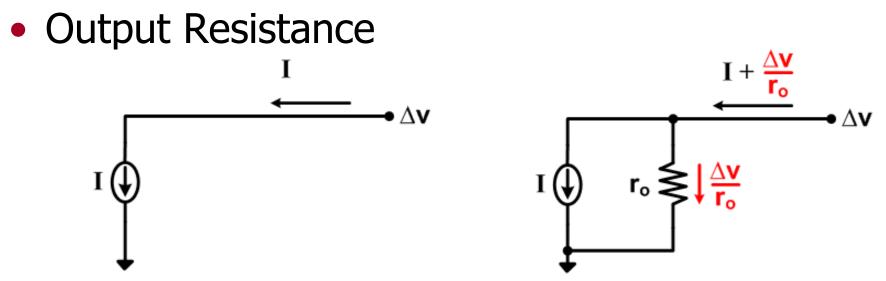

### Small-Signal Output Resistance: Simple Current Mirror/Source (Finite r<sub>o</sub>)

- A simple current mirror/source has an output resistance equal to a single transistor r<sub>o</sub>

- In order to maintain a high output impedance we need a minimum output compliance voltage

Compliance Voltage =  $V_{DSAT2} = V_{GS2} - V_{T2}$

rout

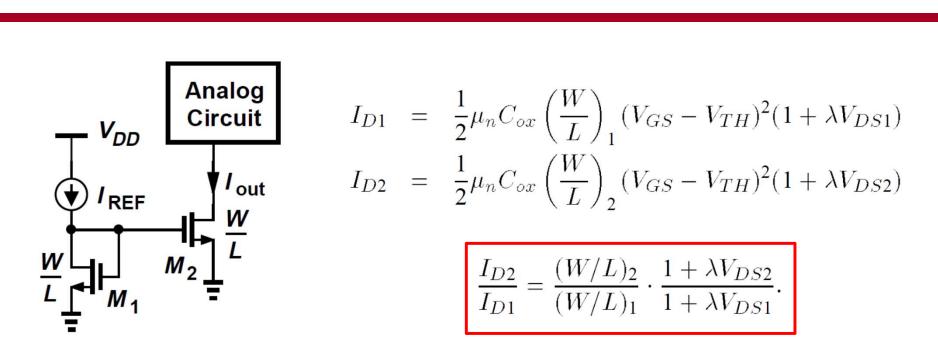

# Simple Current Mirror Accuracy

- While  $V_{DS1} = V_{GS1} = V_{GS2}$ ,  $V_{DS2}$  may not equal  $V_{DS1}$

- This causes an error in the mirroring ratio

- To improve accuracy we can (a) force  $V_{DS2}$  to be equal to  $V_{DS1}$  (Cascode Current Mirror), or (b) force  $V_{DS1}$  to be equal to  $V_{DS2}$  (Low-Voltage Cascode Current Mirror)

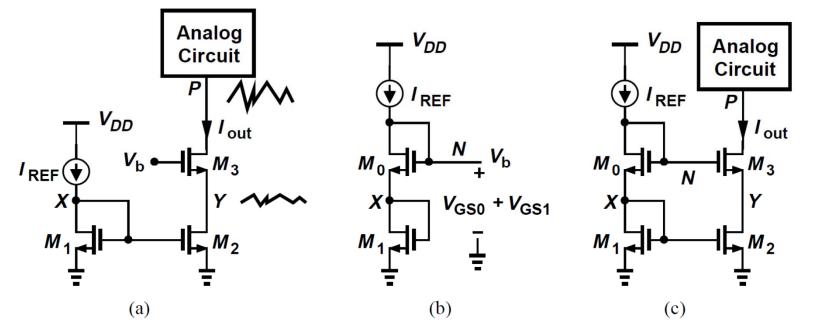

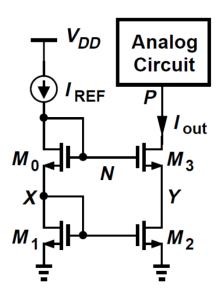

### **Cascode Current Mirror**

- A cascode device can shield a current source, thereby reducing the voltage variations across it.

- But, how do we ensure that  $V_{DS2} = V_{DS1}$ ?

- We can generate  $V_b$  such that  $V_b V_{GS3} = V_{DS1}(= V_{GS1})$ with a stacked diode connected transistor

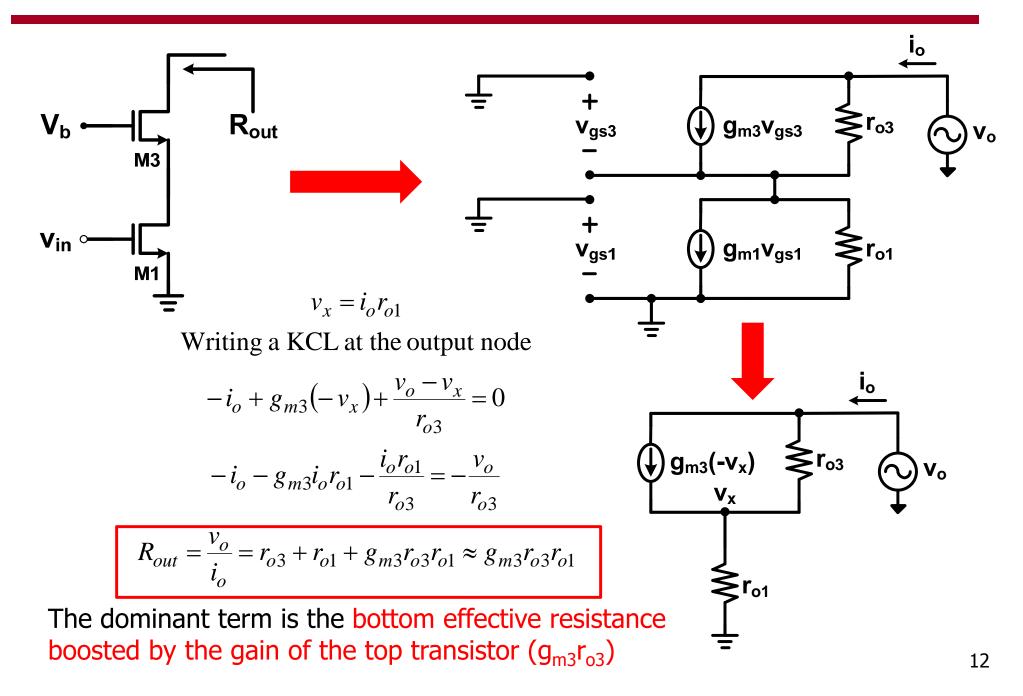

#### MOS Cascode Topology Output Resistance

### Cascode Current Mirror Compliance Voltage

What is the minimum output voltage V<sub>P</sub> such that all the output transistors remain in saturation?

$$V_P = V_Y + V_{DSAT3} = V_{GS1} + V_{GS3} - V_T$$

Compliance Voltage =  $V_{GS1} + V_{DSAT3}$

• Note that this output stage biasing technique "wastes" one threshold voltage, as  $V_Y$  could potentially be lower by a  $V_T$  and  $M_2$  would still be in saturation

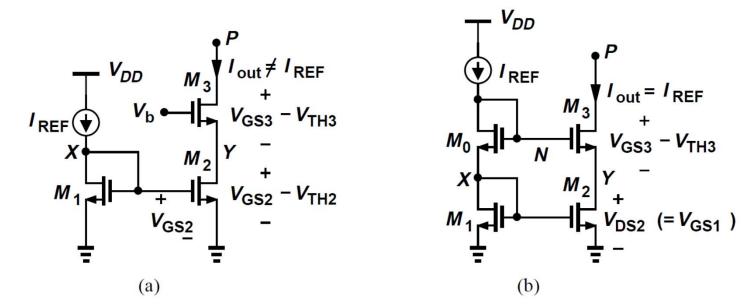

### How Can We Get a Lower Compliance Voltage?

- The left figure uses the minimum possible  $V_b$  such that  $M_2$  and  $M_3$  remain in saturation

- However, as  $V_X \neq V_Y$ , the output current does not accurately track  $I_{REF}$

- The right figure (our original cascode current mirror) achieves good accuracy, but again wastes a threshold voltage relate to the left figure

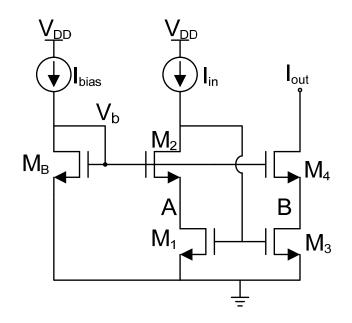

### Low-Voltage Cascode Current Mirror

**Compliance Voltage** =  $V_{DSAT3} + V_{DSAT4}$

- M2 and M4 should be sized such that

- $V_{GS2} = V_{GS4}$

- M1 and M3 biased near edge of saturation

- $V_{DS1} \approx V_{DS3} \approx V_{DSAT}$

- $V_b = V_{GS2} + (V_{GS1} V_{T1}) = V_{GS4} + (V_{GS3} V_{T3})$

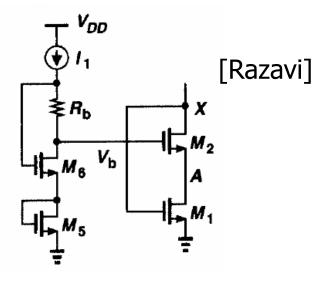

# Alternative V<sub>b</sub> Generation

- Saves one current branch

- M5 sized such that  $V_{GS5} \approx V_{GS2}$

- Some body effect error here

- Size M6 and Rb such that

•

$$V_{DS6} = V_{GS6} - R_b I_1 \approx V_{GS1} - V_{T1}$$

### Next Time

Table-Based Design